Bu teknik doküman B107AA R6 için hazırlanmış olup yeni yapılacak olan tasarımlara kaynak niteliğindedir.

Enerji Analizörü İşlemcisi

Genel Bakış

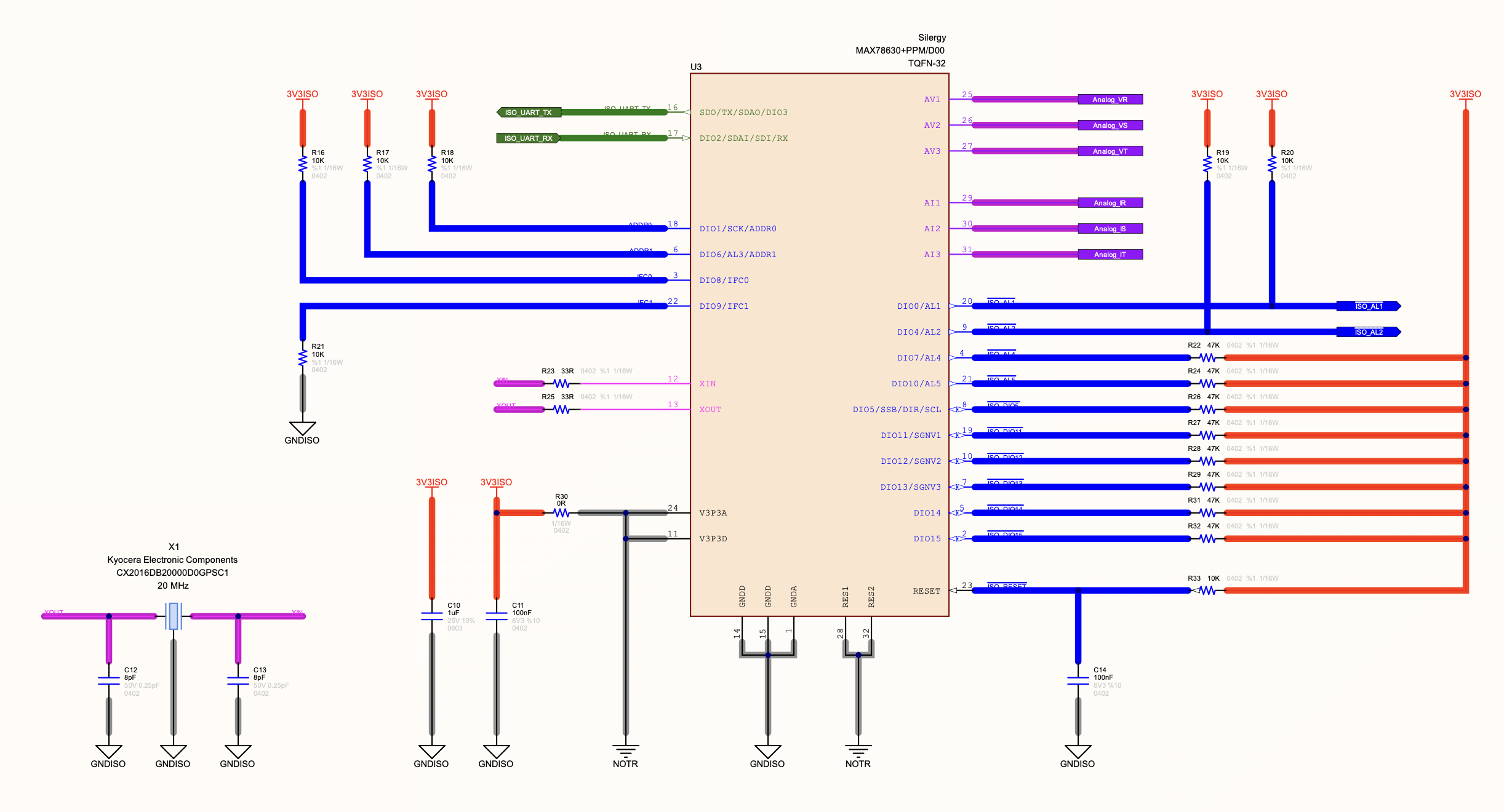

Bu sistem, tarımsal arazilerde bulunan enerji verilerinin tamamını sahadan toplayıp, güvenilir ve doğrulanabilir ölçümlerle anlamlandırmak amacıyla tasarlanmıştır. Çevresel koşullar (uzun hatlar, HV transient’leri, elektromanyetik gürültü, toprak döngüleri) nedeniyle ölçüm katmanının referans bütünlüğünü korumak kritik olduğu için, R6 revizyonunda ölçüm katmanı ile ana MCU arasına tam izole UART/SSI haberleşme bariyeri yerleştirilmiştir.

Bu doküman; MAX78630 tabanlı ölçüm SoC çevresini (arayüz seçimi/strap, saat, reset, besleme, dijital hatlar) mühendislik gerekçeleriyle açıklarken, analog voltaj (AV1/AV2/AV3) ve akım (AI1/AI2/AI3) girişlerinin ön devrelerinin ayrı sayfalarda ele alındığını vurgular. Alarm hatları AL1 ve AL2 izole tarafta işlemciye taşınır; varsayılan aktif‑LOW davranış ve harici pull‑up ile sahada kararlı HIGH bekleme, olayda LOW seviye elde edilmesi hedeflenir.

Arayüz ve strap seçimleri, MAX78630 datasheet’teki IFC0/IFC1 örnekleme mantığına uygun olarak yapılır (UART/SSI için IFC0=1, IFC1=0). Donanımsal adresleme için ADDR0/ADDR1 pull‑up ile sabitlenir. Boştaki veya kullanılmayacak DIO hatları firmware tarafından input bırakılır ve harici 47 kΩ pull‑up ile sahada kararlı 1 seviyesine oturtulur. Strap ve güçlü alarm pull‑upları için 10 kΩ seçimi, gürültü bağışıklığı ile güç tüketimi arasında iyi denge sağlar. Örnek akım hesabı:

Saat kaynağı olarak 20 MHz kristal kullanılır ve seçilen kristalin CL değerine göre yük kapasitörleri belirlenir; ayrıntılı hesap ve gerekçeler “Saat Kaynağı” bölümünde verilmiştir. İzolasyon mimarisiyle ölçüm doğruluğu korunurken, sahadaki HV gürültüler ve röle/modem kaynaklı transient’ler izole tarafta yönetilir.

Mimari Özet

B107AA‑R6 ölçüm katmanı, MAX78630 tabanlı 3‑faz enerji ölçüm SoC etrafında aşağıdaki mühendislik bloklarından oluşur:

-

Analog girişler:

- AV1/AV2/AV3: Faz gerilimleri (VR/VS/VT) — gerilim bölücü ön katmandan gelir.

- AI1/AI2/AI3: Faz akımları (IR/IS/IT) — CT/burden ve RC anti‑alias ile hazırlanır.

-

Dijital hatlar / yardımcı I/O:

- AL1/AL2: İzole taraftan işlemciye taşınır; varsayılan aktif‑LOW, harici 10 kΩ pull‑up ile kararlı HIGH bekleme sağlanır.

- SGNV/DIO yardımcı hatlar: Boştaki hatlar firmware’de input bırakılır; harici 47 kΩ pull‑up ile sahada kararlı “1” seviyesi elde edilir.

-

İzole haberleşme (UART/SSI): Ana MCU ile ölçüm SoC arasındaki haberleşme ISO UART üzerinden yürütülür. Strap mantığı datasheet’e uygundur: IFC0=1 (10 kΩ PU), IFC1=0 (10 kΩ PD); donanımsal adresleme için ADDR0/ADDR1=1 (10 kΩ PU).

-

Saat (clock) kaynağı: Harici 20 MHz kristal (X1) kullanılır; kristal CL değerine göre yük kapasitörleri seçilir ve XIN/XOUT hatlarına seri sönümleme dirençleri eklenir. Ayrıntılı hesap “Saat Kaynağı” bölümünde verilir.

-

Besleme ve topraklama: İzole ölçüm tarafı 3V3ISO ile beslenir; V3P3A (analog) ve V3P3D (dijital) ayrımı korunur. U3’e yakın 100 nF HF decoupling ve 1 µF lokal bulk kullanılır. Dağıtım köprüsü R30 (0 Ω), gerekirse ferrite bead ile EMI/jitter iyileştirmesine açıktır. GNDA/GNDD dönüşleri GNDISO plane üzerinde kontrollü birleştirilir.

Bu sayfa yalnızca SoC çevresi (pin strap, clock, reset, besleme, dijital hatlar) kısmını dokümante eder. Gerilim/Akım analog girişlerinin ön devreleri ilgili sayfalarda detaylandırılır: Gerilim Girişi, Akım Girişi ve İzole Haberleşme.

MAX78630

- Parça: MAX78630+PPM/D00 (3‑faz enerji ölçüm SoC)

- Paket: TQFN‑32

- Besleme: V3P3A (analog) + V3P3D (dijital), 3.0–3.6 V aralığı

- Tipik akım: Normal operasyonda toplam ~8.1–10.3 mA (V3P3A+V3P3D bileşik)

- AFE giriş aralığı: Her analog giriş, V3P3A referansına göre ±250 mVpk (sinüs için ≈176.78 mVrms)

Bu sayfa, MAX78630’un SoC çevresi (arayüz seçimi/strap, saat, reset, besleme, dijital I/O ve bring‑up) kararlarını datasheet ile uyumlu şekilde sabitler. Analog girişlerin (gerilim bölücü + CT/burden + anti‑alias RC) ayrıntıları ayrı sayfalarda ele alınır.

Haberleşme Arayüzü ve Pin Strap Mantığı

MAX78630 üzerinde haberleşme pinleri çoklanmıştır (mux). Bu revizyonda şematik bağlantısı UART (SSI protokolü) modunu hedefler:

- ISO_UART_TX → U3 pin 16 (SDO/TX/SDAO/DIO3)

- ISO_UART_RX → U3 pin 17 (SDI/RX/SDAI/DIO2)

İzolasyon ve veri hızı bütçesi

Saha izolasyonu, doğruluk ve güvenlik için zorunludur. İzole UART hattında seçilecek veri hızı B için bit süresi:

Tipik bir dijital izolatörün yayılım gecikmesi sınıfındadır. Örnek hız bütçesi:

Bu, 500 kbaud–1 Mbaud aralığında güvenli çalışmayı destekler. Daha yüksek hızlarda hat bütünlüğü, izolatör modeli ve jitter bütçesi birlikte doğrulanmalıdır.

Arayüz seçimi (IFC0 / IFC1)

Datasheet’e göre IFC0 ve IFC1 pinleri reset sonunda örneklenir ve seri arayüz şu şekilde seçilir:

| IFC0 | IFC1 | Seçilen arayüz |

|---|---|---|

| 0 | X | SPI |

| 1 | 0 | UART / RS‑485 (SSI) |

| 1 | 1 | I2C |

Bu kartta hedef UART olduğu için:

- IFC0 = 1 → R16 = 10 kΩ pull‑up (3V3ISO)

- IFC1 = 0 → R21 = 10 kΩ pull‑down (GNDISO)

Not (kritik): Datasheet, IFC/ADDR pinleri doğrudan GND/V3P3D’ye bağlanacaksa bu pinlerin yazılım tarafından input olarak bırakılmasını şart koşar. Biz harici pull‑up/pull‑down ile “strap” yaptığımız için bu risk pratikte minimize edilir; yine de firmware tarafında bu pinlerin input kalması iyi pratiktir.

Strap düğüm dinamiği (RC kararlılığı)

Strap düğümlerinin reset örneklemesi sırasında kararlı seviyeye ulaşması için, düğüm zaman sabitinin küçük seçilmesi gerekir. Harici direnç R_{strap} ve tahmini düğüm kapasitansı C_{node} ile:

Örnek olarak ve varsayımında:

Genelde 5τ ≈ 1 µs içinde seviye tam oturur; bu nedenle 10 kΩ seçimi, reset bitişindeki örneklemeye kadar kararlı mantık seviyesi sağlar. 47–100 kΩ değerlerde τ büyür ve sahada kapasitif kuplajlı gürültüye duyarlılık artar.

Adres pinleri (ADDR0 / ADDR1)

UART (SSI) ve I2C modlarında cihaz adreslemesi için iki donanımsal pin kullanılır:

- ADDR0: U3 pin 18 (SCK/ADDR0/DIO1)

- ADDR1: U3 pin 6 (AL3/ADDR1/DIO6)

Bu iki pin, reset sonunda örneklenerek başlangıç adresleme davranışına katkı verir ve UART çoklu‑nokta (multi‑point) senaryosunda DEVADDR alanı ile birlikte kullanılır.

Bu kartta:

- ADDR0 = 1 → R18 = 10 kΩ pull‑up (3V3ISO)

- ADDR1 = 1 → R17 = 10 kΩ pull‑up (3V3ISO)

Tek hedefli (point‑to‑point) kurulumda adres pinleri işlevsel olarak kritik değildir; ancak üretim varyasyonlarında aynı yazılımın farklı kartlarda çakışmasız çalışması için donanımsal adres sabitleme faydalıdır.

Yük akımı ve mantık marjı

Pull‑up ile sabitlenen bir adres pininde, giriş kaçak akımı I_{leak} varsayımıyla düğüm gerilimi:

Örnek: , , için:

Tipik CMOS eşik kabul edilirse ve marj ile güvenli seviyededir. Bu nedenle 10 kΩ, adres/strap için iyi bir güvenlik payı sağlar.

Strap direnç değeri seçimi (10 kΩ)

10 kΩ, gürültü bağışıklığı ile güç tüketimi arasında iyi denge sağlar:

- Strap pini LOW’a çekilirse maksimum akım:

- 47–100 kΩ gibi çok daha büyük değerler, HV gürültülü sahada pinin “yarı‑floating” davranmasına daha yatkındır.

Gürültü bağışıklığı – akım tüketimi dengesi

Gürültü bağışıklığı harici empedansla ters orantılıdır. 10 kΩ, sahadaki kapasitif kuplajlı darbe akılarını hızla sönümleyip düğümü sabitleyebilirken, akım bütçesinde kabul edilebilir bir yük oluşturur. Ayrıca alarm hatları için 10 kΩ seçimi, aktif‑LOW davranışta LOW → olay geçişlerinde belirgin ve hızlı kenarlar sağlar; yardımcı I/O’da 47 kΩ ile bekleme akımı azaltılır.

Alarm Hatları (AL1/AL2)

AL1/AL2 hatları olay/interrupt amaçlıdır. Varsayılan yaklaşım: aktif‑LOW davranış ve 10 kΩ pull‑up (3V3ISO) ile HIGH’da bekleme; olayda LOW’a çekilerek yakalama. Eğer AL hatları izolasyon bariyerini geçerek MCU’ya gidiyorsa, giriş tarafında Schmitt‑trigger özellikli isolator/MCU girişleri tercih edilir.

Direnç seçimi ve akım/power hesabı

LOW durumda AL sürücüsü üzerinden geçen akım:

Sürücünün termal güvenliği için üst sınır yaklaşımıyla güç:

Pratikte sürücü üzerindeki düşüm çok daha küçük olduğundan gerçek güç daha düşük olacaktır; yine de bu üst sınır tasarım açısından güvenlidir.

Yükselme/zayıflama süresi ve RC modeli

AL düğümünün efektif kapasitansı (pin + iz + isolator/MCU girişi) varsayılsın. Yükselme zamanı (10–90%) yaklaşık:

Örnek: , → , .

VIH eşiğini (ör. ) geçiş süresi:

Bu süreler, izolasyon gecikmesi (tipik ) ile birlikte < 1 µs mertebesinde toplam gecikme sağlar; alarm yakalama için yeterlidir. 47 kΩ kullanılsaydı ~ 3.1 µs’e çıkar; bu nedenle AL hatlarında 10 kΩ tercih edilir.

Debounce / deglitch seçenekleri

- Donanım: AL hattına 33–100 Ω seri direnç + 100 pF–1 nF küçük kapasitör ile girişte RC deglitch uygulanabilir. Kesim frekansı:

Örnek: , → ; HF gürültü bastırılırken alarm kenarı hala hızlıdır. Unutmayın ki bu kapasitör, ’a eklenerek ’yi artırır; değerler buna göre seçilmelidir.

- Yazılım: MCU’da düşen kenarda interrupt + asgarî darbe genişliği filtresi (örn. ) uygulanması önerilir.

EMC/ESD ve yerleşim

- Hatlar kart içinde kalıyorsa ek ESD çoğu durumda gerekmez; bariyeri veya konektörü geçiyorsa düşük C TVS (TPD2E2U06 vb.) konnektöre yakın yerleştirilebilir.

- Pull‑up (10 kΩ) 3V3ISO’ya yakın ve iz kısa olmalıdır. AL hatları yüksek dv/dt bölgelerinden uzak tutulur.

Doğrulama ve gecikme bütçesi

- Osiloskopla AL düğümünde ve ölç.

- İzolatör çıkışında propagasyon gecikmesi ’yi ekleyerek uçtan uca gecikmeyi doğrula.

- MCU tarafında minimum darbe genişliği (interrupt yakalama) limitini deneysel olarak belirle ve dokümante et.

Kullanılmayan Pinler

Bu bölüm, MAX78630 çevresindeki kullanılmayan dijital pinlerin sahada kararlı ve düşük güç tüketimi ile nasıl bağlanacağını özetler.

Dijital I/O (DIO/SGNV/yardımcı hatlar)

- Firmware’de yönü

inputbırakın (yüksek empedans). Datasheet’e göre input bırakılan DIO’da iç pull‑up mevcut olsa da sahada kararlılık için harici zayıf pull‑up/pull‑down önerilir. - Varsayılan seviye gereksinimine göre:

- Kararlı HIGH bekleme: 47 kΩ pull‑up (3V3ISO)

- Kararlı LOW bekleme: 47 kΩ pull‑down (GNDISO)

- Alarm hatları (örn. AL1/AL2) için olay yakalama performansı ve kenar hızı amacıyla 10 kΩ pull‑up kullanın (aktif‑LOW varsayılanıyla HIGH’da bekler, olayda LOW’a çekilir).

RC zaman sabiti (kararlılık)

Harici direnç R ve düğümün efektif kapasitansı C_{node} (pin kapasitansı + PCB parasitikleri) için zaman sabiti:

Örnek: , ise:

Genel I/O bekleme için bu yeterlidir. Strap/örnekleme pinlerinde ise 10 kΩ tercih edilir (daha küçük ile daha hızlı kararlılık).

Kaçak akım altında düğüm gerilimi

Giriş kaçak akımı ile pull‑up kullanıldığında düğüm gerilimi:

Örnek: , , için:

Tipik CMOS eşik kabul edilirse ; marj yüksek ve güvenlidir.

Bekleme akımı bütçesi

Harici pull‑up ile beklemede çekilen akım, pin sayısı N için:

Örnek: , , :

Güç bütçesi hassas ise, 47 kΩ ile düşük akım korunur; 10 kΩ sadece hız/kenar belirginliği gereken hatlarda (AL1/AL2, strap) tercih edilir.

Strap ve adres pinleri notu

- IFC0/IFC1 ve ADDR0/ADDR1 pinleri “kullanılmayan” olarak değerlendirilmez; reset örneklemesinde kararlı seviye şarttır. Bu nedenle:

- IFC0 = 1: 10 kΩ pull‑up (3V3ISO)

- IFC1 = 0: 10 kΩ pull‑down (GNDISO)

- ADDR0/ADDR1 = 1: 10 kΩ pull‑up (3V3ISO)

Reserved pinler (RES1 / RES2)

Datasheet, RES1 (pin 28) ve RES2 (pin 32) için açıkça şunu ister: V3P3A’ya bağlayın (Tie to V3P3A).

R6 şemasında bu pinler NOTR ağına düşmüş görünüyor. Bu dokümanla birlikte tasarım kararı şu şekilde sabitlenmiştir:

- RES1, RES2 → V3P3A (3V3ISO)

Neden V3P3A’ye bağlanmalı?

- İç bias/topoloji uyumu: RES pinleri SoC içindeki analog bias/topolojiye referans verir. Analog rail’e (V3P3A) bağlamak, iç blokların beklenen bias rejiminde çalışmasını garanti eder.

- Floating riskinin önlenmesi: Boşta bırakılmış pinler PCB’de anten gibi davranarak EMI/ESD kuplajına açık kalır; iç lojik/analog bloklarda kararsız moda riskini artırır.

- Datasheet uyumu: V3P3D veya GND yerine V3P3A şartı, iç ayrımı (analog/dijital) korumak ve gürültü marjını maksimize etmek içindir.

Uygulama ve üretim denetimi

- Bağlantı yöntemi: İki ayrı 0 Ω köprü veya doğrudan net birleşimi ile V3P3A’ya çekin; RC veya yüksek değerli direnç kullanmayın.

- Yerleşim: U3’e yakın, kısa hat ve V3P3A plane’e en düşük empedanslı dönüş ile bağlayın.

- DFM/DFT kontrolü: Üretimde optik muayene (0 Ω yerinde mi?) + basit süreklilik testi ile doğrulayın. ECO gerektirirse 0 Ω pad’li çözüm sahada esneklik sağlar.

Kaçak akım ve güç etkisi (tahmin)

Her reserved pin için tipik giriş kaçak akımı kabul edelim. Toplam kaçak:

Örnek: ise . Güç:

Toplam SoC akımına (≈8.1–10.3 mA) oranı:

Sonuç: V3P3A’ye sabit bağlama, güç bütçesinde ihmal edilebilir etkiyle maksimum kararlılık sağlar.

Ramp‑up ve sıralama notu

RES1/RES2 doğrudan V3P3A’ye bağlı olmalı; seri RC/PD kullanılmamalıdır. V3P3A rampingi sırasında iç bloklar analog rail’i takip eder; ek zaman sabitleri tanımlamamak reset/bring‑up deterministiğini artırır.

Uygulama pratikliği için önerilen bağlama:

- RES1/RES2 için iki ayrı 0 Ω köprü (veya tek bir net birleşimi) ile 3V3ISO’ya çekme.

Bu, üretimde “unutulmuş/boşta” pin riskini ortadan kaldırır ve datasheet ile tam uyum sağlar.

Saat Kaynağı

U3 XIN/XOUT pinleri, harici 20 MHz kristal ile sürülür:

- X1: 20 MHz kristal (Kyocera CX2016DB20000D0GPSC1)

- C12, C13: 8 pF (GNDISO’ya)

- R23, R25: 33 Ω seri (XIN ve XOUT hatlarında)

Yük kapasitörü hesabı (datasheet + seçilen kristal ile)

MAX78630 datasheet, 20 MHz kristal için iki adet yük kapasitörünü tipik 18 pF olarak örnekler; ancak bu değer kristalin hedef CL değerine ve kartın parazitiklerine göre ayarlanmalıdır.

Genel yaklaşım:

Simetrik seçimde (C1=C2=C):

Bu tasarımda seçilen kristal (Kyocera CX2016DB… varyantı) CL = 8 pF sınıfındadır. Datasheet ayrıca XIN ve XOUT pinlerinin GNDD’ye göre yaklaşık 5 pF kapasitans taşıdığını belirtir.

Pratik hesap için her iki tarafta toplam kapasitansı şöyle ele alırız:

Örnek: C12=C13=8 pF, pF, pF varsayımıyla:

- pF

- pF

Dolayısıyla kristalin gördüğü efektif yük:

Bu değer, 8 pF CL kristal için hedefe oldukça yakındır.

Alternatif: Eğer CL=12 pF gibi daha yaygın kristal kullanılacaksa, C12/C13 değerlerini 18 pF civarına çekmek (datasheet’in önerdiği tipik değer) çoğu yerleşimde doğru noktaya oturur.

Seri 33 Ω dirençler ne işe yarar?

R23/R25, kristal sürüşünde:

- sürücü–kristal arasındaki çınlama/overshoot riskini azaltır,

- EMI yayılımını düşürür,

- bazı kristal/PCB kombinasyonlarında başlatma kararlılığını iyileştirir.

33 Ω, pratikte “güvenli başlangıç” değeridir. Sahada start-up problemi görülürse 0–100 Ω aralığında optimizasyon yapılabilir.

Başlatma (start‑up) ve sürüş seviyesi

- Start‑up gözlemi: XOUT üzerinde zarf (envelope) büyümesi sürekli ve monotondur; birkaç milisaniye içinde genlik kararlı seviyeye oturur. 33 Ω ile başlatma güvenliği artar; genlik temporer düşük olabilir.

- Sürüş seviyesi (drive level): Kristal datasheet’inde tipik maks. 100 µW sınırlaması bulunur. Güvenli yaklaşım: genlik yüksek ise seri direnç 33→68 Ω aralığında artırılarak sürüş seviyesini düşürmek.

- Ölçüm yöntemi (pratik): Yüksek empedanslı prob ile XOUT Vpp ölçülür; sahada ayrıca MCU timer/capture ile frekans doğrulanır. Sürüş seviyesi doğrudan ölçülmez; değerlendirme, genlik ve start‑up davranışı üzerinden yapılır.

Frekans doğrulama ve ppm hesabı

Nominal frekans . Ölçülen frekans ile sapma:

Örnek: ise ve .

Toplam frekans bütçesi; kristal toleransı (25 °C), sıcaklık kararlılığı ve yaşlanma bileşenlerinden oluşur. Yük kapasitörü CL sapması da paralel rezonans frekansını ppm düzeyinde etkiler; doğrulama timer/capture ölçümleriyle yapılır.

Yerleşim ve EMI önerileri

- Kısa hat: XIN/XOUT hatlarını en kısa ve simetrik tutun.

- Kaplar: CL kapasitörleri NP0/C0G sınıfında ve toleransı düşük seçin; XIN/XOUT’a eşit değer kullanın.

- Toprak gölgeleme: XIN/XOUT altında sürekli GNDISO plane; kesintisiz dönüş yolu.

- Ayrık yerleşim: Kristal ve kapasitörleri U3’e olabildiğince yakın yerleştirin; uzun hat/branch bırakmayın.

Saha doğrulama prosedürü (özet)

- Frekans ölçümü: MCU timer/capture ile 20 MHz doğrulanır;

ppmhesabı yapılır. - Genlik gözlemi: Osiloskop ile XOUT Vpp ölçülür; start‑up zarfı ve kararlılık kontrol edilir.

- Seri direnç optimizasyonu:

R23/R25değerleri 0–68 Ω aralığında denenerek start‑up kararlılığı ve EMI gözlemleri optimize edilir. - CL doğrulaması: Kapasitör tolerans/seri etkileri ile efektif CL hesabı gözden geçirilir; gerekirse ±2 pF varyasyon ile deneme.

Besleme ve Decoupling

MAX78630, izole ölçüm tarafında 3V3ISO ile beslenir ve iki ayrı besleme pini vardır:

- V3P3A (pin 24): Analog besleme

- V3P3D (pin 11): Dijital besleme

İzole 3V3ISO kaynağı ve hesap detayları, güç mimarisi sayfasında dokümante edilmiştir: Enerji Analizör Besleme. Özetle topoloji: 5V → (izole DC/DC) → 5V_ISO → (AP2112K‑3.3) → 3V3_ISO; ray üzerinde C52=22µF bulk ve C53=100nF HF bypass kullanılır.

Güç bütçesi

Datasheet’e göre normal operasyonda toplam akım (V3P3A+V3P3D bileşik) ~8.1–10.3 mA seviyesindedir. Güç mimarisi sayfasındaki tasarım varsayımlarına göre izole 3V3 tarafı için hedef bütçe:

Bu marj, MAX78630 + izolatör + yardımcı lojik geçişlerinde LDO ve DC/DC’nin termal/regülasyon davranışını rahat tutar. LDO kaybı için (5V_ISO→3V3_ISO):

Örnek: I=50 mA için P_LDO ≈ 85 mW.

Decoupling yerleşimi

R6’da besleme dağıtımı şu mantıkla ele alınır:

- C11 = 100 nF: U3’e en yakın HF decoupling

- C10 = 1 µF: U3 çevresinde lokal bulk

- R30 = 0 Ω: 3V3ISO dağıtım köprüsü

R30 footprint’i, sahada analog ölçümde jitter/EMI etkisi görülürse ferrite bead ile iyileştirmeye açıktır.

Zaman ölçeklerine göre yerel gerilim sapması yaklaşık:

- Çok hızlı kenarlar (ör. ) için C11=100 nF:

- Orta zaman ölçekleri (ör. ) için yerel C10=1 µF tek başına:

Bu durumda ray bulk’u (C52=22 µF) devreye girer ve aynı senaryoda:

Sonuç olarak, C11 çok hızlı bileşenleri, C10 yakın çevreyi, C52 ise düşük/orta frekanslı yük geçişlerini sönümleyerek toplam sapmayı mühendislik olarak kabul edilebilir seviyede tutar.

0 Ω yerine ferrite bead opsiyonu

Analog/dijital ayrıştırmayı artırmak için R30 yerine:

- 600 Ω @ 100 MHz sınıfında bir ferrite bead

kullanılabilir. Bu durumda V3P3A tarafına ayrı bir 100 nF + 1 µF daha eklemek (yerleşimde mümkünse) analog gürültü tabanını düşürür.

Reset Devresi

MAX78630’un RESET girişi datasheet’e göre gürültü filtrelidir ve harici resetin tetiklenmesi için RESET’in en az 1 µs LOW tutulması gerekir. Reset başlatıldıktan sonra, RESET tekrar HIGH olsa bile cihaz reset modunda 4096 clock cycle daha kalır.

20 MHz saat ile bu iç reset penceresi yaklaşık:

R6’da RESET hattı harici RC ile “yumuşak” bırakılacak şekilde tasarlanmıştır:

- R33 = 10 kΩ pull‑up (3V3ISO)

- C14 = 100 nF (GNDISO)

Zaman sabiti:

Reset hattının pratikte güvenli HIGH seviyesine oturması için ~3τ alınır:

- Yaklaşık 3 ms sonra RESET serbest kalmış kabul edilir.

Bu yaklaşım, sahadaki besleme “bounce” ve izolasyon tarafı gürültülerinde deterministik boot davranışı sağlar.

Reset hedefleri ve zamanlama bütçesi

Amaçlar:

- Harici reset periyodu, datasheet’teki en az LOW süresi olan 1 µs’yi güvenle aşmalı.

- Reset salındıktan sonra iç reset penceresi (20 MHz’te ≈ 204.8 µs) tamamlanana dek sistem kararlı kalmalı.

- 3V3ISO rampasında ve olası “dip” olaylarında reset hattı yalancı eşik geçişlerine (glitch) dirençli olmalı.

RC eşik hesabı

RC ile şarj olan reset düğümü için adım yanıtı:

Reset’in “LOW bölgesinden çıkış” anı için (ör. ):

Örnek: R=10 kΩ, C=100 nF → τ=1 ms ve k_L=0.3 (0.3·VDD ≈ VIL,max) için:

Aynı şekilde “HIGH kabulü” (ör. , tipik k_H≈0.7) için:

Sonuç: 10 kΩ + 100 nF ile harici LOW süresi >> 1 µs ve HIGH’a yükseliş de yumuşak/kararlı gerçekleşir.

Yavaş besleme rampası etkisi

3V3ISO lineer rampa ile yükseliyorsa (ör. ), düğüm gerilimi yaklaşık olarak davranışını izler. Güvenli tasarım için pratik kural:

- 3V3ISO rampasında “reset LOW süresi”nin (VIL,max’a ulaşana kadar geçen süre) ≥ 5·τ_internal_reset + 1 µs olacak şekilde τ’yi küçük tutmak (10 kΩ tercihinin gerekçesi) ve gerekiyorsa C14’ü 100 nF civarında sınırlamak.

Saha doğrulamasında, VDD ve RESET aynı anda ölçülerek “VDD kararlı olmadan önce RESET’in HIGH olmaması” şartı kontrol edilir.

Saha doğrulama

- CH1: 3V3ISO, CH2: RESET. Güç verildiğinde ve zamanlarını ölç.

- İzole DC/DC yük darbesi vererek RESET üzerinde glitch gözle (olursa C14/R33 veya supervisor ile gider).

- MCU tarafı bring‑up’ta ilk haberleşme (UART/SSI) penceresini, iç reset penceresi (≈ 204.8 µs) sonrasına yerleştir.

Analog Girişler (Özet)

- AV1/AV2/AV3 → Analog_VR / Analog_VS / Analog_VT — Ayrıntılar ve bölücü/kalibrasyon: Gerilim Girişi

- AI1/AI2/AI3 → Analog_R / Analog_S / Analog_T — Ayrıntılar ve CT/burden/RC: Akım Girişi

Analog hatlar, ölçüm doğruluğu için şu kurallarla PCB’de yürütülmelidir (detaylı kılavuz ilgili sayfalarda yer alır):

- HV switching hatlarından uzak,

- mümkün olduğunca kısa,

- analog referans/ground dönüşü kontrollü,

- girişlerde RC filtre/kompanzasyon elemanları (ilgili sayfada) ile uyumlu.

Topraklama (GNDISO / GNDA / GNDD)

U3 üzerinde GNDA ve GNDD pinleri bulunur. İzole ölçüm tarafında bu pinler, kart genelinde GNDISO altında yönetilir. Hedef; tek ve süreklilik arz eden bir referans düzlemi üzerinden dönüş akımlarını kontrol ederek ölçüm doğruluğunu ve EMC dayanımını artırmaktır.

Felsefe: Sürekli plane + yönlendirilmiş dönüş

- Tek parça GNDISO plane: U3 ve çevresinde plane’i bölmeyin. Sert bölünmüş analog/dijital toprak çoğu durumda dönüş akım yolunu uzatıp gürültüyü artırır. Bunun yerine dönüş akımlarını hat yerleşimi ve “yerel moat/slot”larla yönlendirin.

- GNDA/GNDD birleşimi: GNDA pinlerinin yakınında (tercihen U3 altındaki ısıl pad/slug çevresinde) GNDA→GNDISO birleşimini kısa ve düşük empedanslı yapın. Ayrı ada/toprak kullanmayın.

- Kısa dönüş yolları: Yüksek dI/dt hatlarının (kristal sürüş, dijital kenarlar) altını kesintisiz GNDISO ile destekleyin; dönüş akımı doğrudan hat altından akabilsin.

Analog girişlerin dönüşü

- Analog ön uç dönüşü: Gerilim bölücü ve CT/burden dönüşlerini mümkün olduğunca GNDA pinlerine yönlendirin; yüksek akım dijital döngülerle ortak dönüş yolu paylaşmayın.

- Yıldız benzeri bağ: Analog giriş ağlarının dönüşünü U3 GNDA bölgesine “yıldız benzeri” kısa yollarla getirin; bu noktadan GNDISO plane’e bağlanır.

Bariyer ve HV alanlar

- İzolasyon bariyeri: GND ↔ GNDISO arasında bakır “köprü” oluşturmayın. Bariyer hattında plane’i geri döndürmeyin; creepage/clearance kurallarını uygulayın (uygulanan standarda göre, ör. IEC 61010/62368).

- Stitching/AC kapasitörler: Bariyer boyunca dikiş vias’ı veya AC “stitching capacitor” kullanmayın; izolasyon bütünlüğünü bozabilir.

- HV çevresi keep‑out: Yüksek gerilim bölgesine yakın GNDISO plane’i gerektiğinde “moat/slot” ile seyrelterek kaçak akımı ve yüzey akımlarını azaltın.

Dekuplaj ve via yerleşimi

- Her kapasitöre bir via: C11/C10 gibi dekuplaj kaplarının GND pad’inden doğrudan GNDISO plane’e en az bir via ile inin; paylaşımlı uzun GND hatlarından kaçının.

- Via yoğunluğu: U3 çevresinde plane‑iletişim vias’ını 5–10 mm aralıklarla kullanın; ray dönüş empedansını düşürür.

- R30/ferrit yolu: R30 hattı üzerinden V3P3A/V3P3D dağıtımında, ferrite bead kullanılıyorsa bead’in GNDISO referansına yakın konumlanmasına ve önce/sonra yerel dekuplaja dikkat edin.

Döngü alanı ve endüktans sezgisi

Kapanan bir akım döngüsünün endüktansı yaklaşık olarak döngü alanı ile artar; dolayısıyla döngü alanını küçültmek yüksek frekans empedansını azaltır:

Bu nedenle yüksek frekans içeren hatların (kristal, AL hatları, UART) referans plane’i üzerinde ve kısa dönüş yollarıyla yönlendirilmesi kritik önemdedir.

Kontrol listesi (pratik)

- U3 altında süreklı GNDISO plane; bölme yok.

- Analog giriş ağlarının dönüşü GNDA bölgesine ve kısa; dijital yüklerle paylaşım yok.

- Bariyerde köprü yok; creepage/clearance sahaya uygun.

- Dekuplaj GND pad’inden doğrudan via; bir kapasitöre bir via.

- Yüksek dI/dt hatlarının altında kesintisiz plane; döngü alanı küçük.

Komponent Seçimi (SoC çevresi)

Bu bölümde, diğer sayfalardaki formatla uyumlu şekilde her bileşen için 3 alternatif tablo halinde verilmiştir. “Seçilen” satırı R6 hedefini gösterir.

SoC (U3)

| Durum | Üretici/Seri | PN | Paket | Not |

|---|---|---|---|---|

| Seçilen | Maxim/ADI | MAX78630+PPM/D00 | TQFN‑32 | Enerji ölçüm SoC |

| Alternatif | Microchip | ATM90E32/36 | — | Mimari değişiklik gerektirir |

| Alternatif | ST | STPM32/STPM33 | — | Mimari değişiklik gerektirir |

Kristal (X1)

| Durum | Üretici/Seri | PN | Frekans | CL | Paket | Not |

|---|---|---|---|---|---|---|

| Seçilen | Kyocera | CX2016DB20000D0GPSC1 | 20 MHz | 8 pF | 2016 | Fundamental |

| Alternatif | Epson | FA‑238 (20 MHz, CL=8 pF) | 20 MHz | 8 pF | 2016 | Eşdeğer |

| Alternatif | TXC | 7A (20 MHz, CL=8 pF) | 20 MHz | 8 pF | 2016 | Eşdeğer |

Not: CL=12 pF kristal seçilirse C12/C13 ≈ 18 pF olmalıdır.

Kristal yük kapasitörleri (C12, C13)

| Durum | Üretici/Seri | PN | Değer | Paket | Dielektrik | Not |

|---|---|---|---|---|---|---|

| Seçilen | Murata GRM | (8 pF, tol. düşük) | 8 pF | 0402 | C0G/NP0 | CL=8 pF ile uyum |

| Alternatif | TDK C | (8 pF) | 8 pF | 0402 | C0G/NP0 | Eşdeğer |

| Alternatif | KEMET C | (8 pF) | 8 pF | 0402 | C0G/NP0 | Eşdeğer |

Kristal seri sönümleme (R23, R25)

| Durum | Üretici/Seri | PN | Değer | Paket | Tolerans | Not |

|---|---|---|---|---|---|---|

| Seçilen | Yageo RC | RC0402 | 33 Ω | 0402 | 1–5% | EMI/çınlama sönümleme |

| Alternatif | Panasonic ERJ | ERJ‑2 | 33 Ω | 0402 | 1% | Eşdeğer |

| Alternatif | Vishay CRCW | CRCW0402 | 33 Ω | 0402 | 1% | Eşdeğer |

Strap/Adres/Alarm 10 kΩ (R16, R17, R18, R19, R20, R21)

| Durum | Üretici/Seri | PN | Değer | Paket | Tolerans | Not |

|---|---|---|---|---|---|---|

| Seçilen | Yageo RC | RC0402 | 10 kΩ | 0402 | 1% | IFC/ADDR/AL pull‑up/pull‑down |

| Alternatif | Panasonic ERJ | ERJ‑2 | 10 kΩ | 0402 | 1% | Eşdeğer |

| Alternatif | Vishay CRCW | CRCW0402 | 10 kΩ | 0402 | 1% | Eşdeğer |

Yardımcı I/O 47 kΩ (R22, R24, R26–R29, R31–R32)

| Durum | Üretici/Seri | PN | Değer | Paket | Tolerans | Not |

|---|---|---|---|---|---|---|

| Seçilen | Yageo RC | RC0402 | 47 kΩ | 0402 | 1% | Zayıf pull‑up (bekleme akımı düşük) |

| Alternatif | Panasonic ERJ | ERJ‑2 | 47 kΩ | 0402 | 1% | Eşdeğer |

| Alternatif | Vishay CRCW | CRCW0402 | 47 kΩ | 0402 | 1% | Eşdeğer |

Besleme köprüsü (R30) / Ferrite bead opsiyonu

| Durum | Üretici/Seri | PN | Tip | Empedans | Paket | Not |

|---|---|---|---|---|---|---|

| Seçilen | — | 0 Ω jumper | Jumper | 0 Ω | 0402 | Varsayılan |

| Alternatif | Murata BLM | BLM18AG601SN1D | Ferrite bead | 600 Ω@100 MHz | 0603 | Analog ayrıştırma |

| Alternatif | Würth | 742792651 | Ferrite bead | 600 Ω@100 MHz | 0603 | Analog ayrıştırma |

Not: Ferrite bead kullanımında yakın dekuplaj şarttır; bead öncesi/sonrası 100 nF + 1 µF tavsiye edilir.

Dekuplaj (C11)

| Durum | Üretici/Seri | PN | Değer | Paket | Dielektrik/Volt | Not |

|---|---|---|---|---|---|---|

| Seçilen | Murata GRM | GRM155 | 100 nF | 0402 | X7R / ≥10 V | HF dekuplaj |

| Alternatif | TDK | C1005 | 100 nF | 0402 | X7R / ≥10 V | Eşdeğer |

| Alternatif | Samsung | CL05 | 100 nF | 0402 | X7R / ≥10 V | Eşdeğer |

Lokal bulk (C10)

| Durum | Üretici/Seri | PN | Değer | Paket | Dielektrik/Volt | Not |

|---|---|---|---|---|---|---|

| Seçilen | Murata GRM | GRM188 | 1 µF | 0603 | X7R / ≥10 V | Lokal bulk |

| Alternatif | TDK | C1608 | 1 µF | 0603 | X7R / ≥10 V | Eşdeğer |

| Alternatif | Samsung | CL10 | 1 µF | 0603 | X7R / ≥10 V | Eşdeğer |

Reset RC (R33, C14)

| Durum | Eleman | Üretici/Seri | PN | Değer | Paket | Not |

|---|---|---|---|---|---|---|

| Seçilen | R33 | Yageo RC | RC0402 | 10 kΩ | 0402 | POR RC |

| Seçilen | C14 | Murata GRM | GRM155 | 100 nF | 0402 | POR RC |

| Alternatif | R33 | Panasonic ERJ | ERJ‑2 | 10 kΩ | 0402 | Eşdeğer |

| Alternatif | C14 | TDK | C1005 | 100 nF | 0402 | Eşdeğer |

| Alternatif | R33 | Vishay CRCW | CRCW0402 | 10 kΩ | 0402 | Eşdeğer |

| Alternatif | C14 | Samsung | CL05 | 100 nF | 0402 | Eşdeğer |

Reserved bağlama (RES1/RES2 → V3P3A)

| Durum | Üretici/Seri | PN | Tip | Paket | Not |

|---|---|---|---|---|---|

| Seçilen | — | 0 Ω jumper | Jumper | 0402 | V3P3A’ya sabit bağlama |

Tahmini Maliyet Analizi (SoC çevresi)

Aşağıdaki tablo, yalnızca SoC çevresi (U3 + clock + strap + reset + decoupling) için tahmini BOM maliyetidir. Varsayımlar: tipik seri üretim (≈1k+) seviye, USD birim fiyatlar, MAX78630 modülü sabit 10.00 USD.

| Kalem | Adet | Açıklama | Birim (USD) | Ara Toplam (USD) |

|---|---|---|---|---|

| MAX78630 | 1 | MAX78630+PPM/D00 | 10.00 | 10.00 |

| Kristal | 1 | 20 MHz, 2016, CL=8 pF | 0.12 | 0.12 |

| Kristal yük C | 2 | 8 pF, 0402, NP0/C0G | 0.015 | 0.03 |

| Seri sönümleme R | 2 | 33 Ω, 0402 | 0.006 | 0.012 |

| Strap/Adres/AL R | 6 | 10 kΩ, 0402 | 0.005 | 0.03 |

| Yardımcı I/O R | 8 | 47 kΩ, 0402 | 0.004 | 0.032 |

| Reset R | 1 | 10 kΩ, 0402 | 0.005 | 0.005 |

| Reset C | 1 | 100 nF, 0402, X7R | 0.010 | 0.010 |

| Decoupling C (HF) | 1 | 100 nF, 0402, X7R | 0.010 | 0.010 |

| Decoupling C (bulk) | 1 | 1 µF, 0603, X7R | 0.030 | 0.030 |

| Köprü (R30) | 1 | 0 Ω, 0402 | 0.002 | 0.002 |

| RES bağlama | 2 | 0 Ω, 0402 (RES1/RES2→V3P3A) | 0.002 | 0.004 |

| Toplam | 10.29 |

İpuçları:

- Fiyatlar tedarikçiye/stoğa göre değişkendir; bu tablo karar/dizayn kıyasına yön vermek içindir.

- 47 kΩ satırı, R30’u içermez (R30 ayrı “Köprü” satırında maliyetlenir).

- Ferrite bead opsiyonu kullanılırsa R30 kalemi yerine ilgili bead birim maliyeti (≈0.03–0.08 USD) yazılmalıdır.