Bu teknik doküman B107AA R6 için hazırlanmış olup yeni yapılacak olan tasarımlara kaynak niteliğindedir.

3V3 Ana Dijital Besleme

Bu sayfa 2026-01-11 tarihinde güncellendi (R6 format + maliyet analizi eklendi).

B107AA‑R6 modülünün dijital/sinyal tarafı yani modül ana beslemesi 3V3 üzerinden çalışır. 3V3 hattı; MCU, I2C haberleşme hatları ve kart üzerindeki düşük güç dijital çevre birimleri için “omurga” niteliğindedir.

R6 mimarisinde 3V3, 5V rayından türetilir ve sabit çıkış AP2112K‑3.3TRG1 (600mA sınıfı CMOS LDO) ile üretilir.

Tasarım hedefleri

| Kalem | Hedef |

|---|---|

| LDO giriş gerilimi | (5V rayı) |

| Çıkış gerilimi | |

| Kullanım profili | 7/24 açık dijital omurga |

| Gürültü hedefi | Dijital rayda düşük ripple / stabil reset davranışı |

| Öncelik | Basitlik + saha güvenilirliği |

R6’da 5V rayı kapanırsa 3V3 de düşer ve sistem resetlenir. Bu davranış mimarinin bir parçasıdır; “3V3 ayrı güç adası” olarak kurgulanmamıştır.

Neden AP2112K?

AP2112K, 3V3 dijital omurga için R6 hedefleriyle uyumlu bir “modern LDO” karakteri sunar:

- Düşük boşta tüketim (Iq): 7/24 açık sistemlerde batarya tarafındaki gereksiz tüketimi azaltır.

- Düşük dropout: 5V rayı düşmeye başladığında 3V3’ün regülasyonda kalma marjı artar.

- Kapasitör esnekliği: Giriş/çıkışta kapasitör ile stabil çalışacak şekilde tasarlanmıştır (X7R/X5R önerilir).

- 600mA sınıfı: MCU + dijital çevre birimleri için geniş bir akım marjı sağlar.

AP2112K (SOT‑25) küçük bir pakettir. 3V3 akımı büyüdükçe aynı kalır fakat ısıyı atmak zorlaşır. Eğer 3V3 hattı sürekli yüksek akım çekecekse, aynı ailede daha termal güçlü paketlere (SOT‑89‑5 / SO‑8) geçiş planlanmalıdır.

Dropout ve minimum giriş gerilimi

Regülasyonda kalmak için yaklaşık koşul:

AP2112K için 3.3V versiyonda tipik dropout şu şekilde ele alınır:

(yüksek yükte)

(yüksek yükte)

Bu durumda yaklaşık minimum giriş gerilimi:

5V tarafı için pratik marj kuralı

Sahada “reset istemiyoruz” hedefi için 5V rayında şu marjı korumak gerekir:

Burada ; transient’ler, kablo düşümü ve ölçüm belirsizliği için bırakılan paydır.

Termal kayıp hesabı

LDO kaybı:

| 3V3 yük akımı () | |

|---|---|

Sıcaklık artışı sezgisi

Isıl artış yaklaşık:

Burada pakete ve PCB bakır alanına bağlıdır. Küçük paketlerde (SOT‑25) daha büyüktür; aynı ’ta daha fazla ısınma görülür.

Kılıf seçim yorumu

- 3V3 akımı 100–250mA bandındaysa, AP2112K ile termal risk genelde yönetilebilir.

- 3V3 akımı 300mA+ seviyelerine çıkıyorsa, SOT‑25 pakette ısınma ve termal marj kritikleşir. Bu durumda aynı regülatör ailesinin SOT‑89‑5 / SO‑8 paketleri tercih edilmelidir.

Kapasitörler ve stabilite

AP2112K, giriş ve çıkışta kapasitör ile stabil çalışacak şekilde tasarlanmıştır. Seramik kapasitör kullanılacaksa X7R/X5R dielektrik tercih edilmelidir.

Seçim kriterleri (R6)

- Gerilim dayanımı (MLCC): 3V3 rayında pratik kural

Bu nedenle 3V3 için MLCC’de 6.3V veya 10V tercih edilir.

- Dielektrik: X7R/X5R; Y5V/Z5U kullanılmaz.

- DC bias: MLCC’de efektif kapasite düşer; bu yüzden 1µF “min” şartı sağlansa bile pratikte seçimi daha güvenlidir.

- Yerleşim: CIN ve COUT mutlaka regülatör pinlerine yakın olmalıdır.

Önerilen kapasitör seti

-

Giriş (5V→LDO):

- Minimum: X7R

- Önerilen: X7R +

-

Çıkış (3V3):

- Minimum: X7R

- Önerilen: X7R +

3V3 hattında “reset istemiyoruz” hedefi için yalnız regülatör çıkışı değil, kritik yüklerin (MCU, haberleşme hatları, RF yardımcı devreleri vb.) yakınına da ek bypass kondansatörleri konumlandırmak sahada fark yaratır.

Komponent seçimi

Regülatör

- U? – AP2112K‑3.3TRG1 (600mA sınıfı, SOT‑25)

Termal marj için paket alternatifi (aynı aile)

Eğer 3V3 akımı büyüyecekse veya kutu içi sıcaklık artacaksa, footprint planlamasında aşağıdaki paketler ciddi avantaj sağlar:

- AP2112R5‑3.3TRG1 (SOT‑89‑5)

- AP2112M‑3.3TRG1 (SO‑8)

Kapasitör seçim parametreleri

- MLCC: X7R/X5R, 6.3V veya 10V, mümkünse 0805/1206 (DC‑bias marjı için)

- Bypass: X7R, 25–50V (genel bypass)

Örnek kapasitör PN yaklaşımı

Bu listede amaç net sınıf tanımlamaktır; stok durumuna göre eşdeğer seçilir:

- CIN / COUT (önerilen): , X7R, 10V, 0805/1206

- CIN / COUT (minimum): , X7R, 10V, 0603/0805

- Bypass: , X7R, 50V

PCB yerleşim notları

- Regülatörün CIN ve COUT kapasitörleri pin dibine yerleştirilir.

- 3V3 dağıtımında dar boğaz bırakılmaz; kritik dijital yüklerin dönüş akımı kısa tutulur.

- SOT‑25 paket için bakır alan küçük kalırsa ısınma artar; mümkün olduğunca GND bakırı genişletilir.

- 3V3 hattı, 5V röle transient’lerinden mümkün olduğunca ayrıştırılır (toprak dönüş yolunu kontrol et).

Ölçüm ve doğrulama

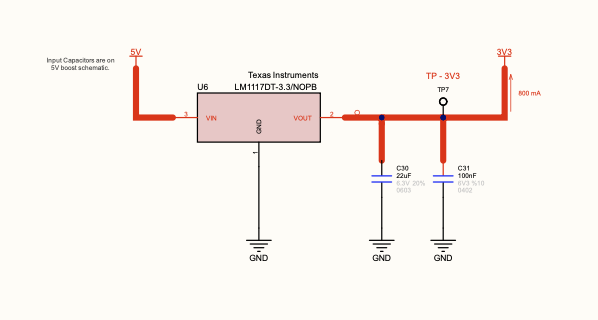

- TP_3V3: Boşta doğrula.

- MCU + dijital yük altında 3V3 droop/ripple ölç.

- 5V üzerinde transient oluştuğunda 3V3 davranışını gözle (reset eşiği ve brown‑out ayarı ile birlikte).

- Regülatör sıcaklığını gerçek saha senaryosunda ölç (kutu içi dahil).

AP2112K alternatifi regülatörler

R6 tasarım hazırlığında amaç; 3V3 hattında kararlılık ve saha güvenilirliğini korurken maliyeti optimum tutmaktır. AP2112K seçimi genel amaçlı bir “denge noktası”dır; aşağıdaki alternatifler ihtiyaç oluşursa değerlendirilir.

Seçim kriterleri

- Kararlılık: MLCC ile stabil çalışabilmeli.

- Dropout / marj: 5V rayı düştüğünde 3V3’ün regülasyondan çıkma eşiği.

- Iq (quiescent): 7/24 açık sistemlerde batarya tüketimi.

- Maksimum akım: 3V3’te tepe/ortalama akım.

- Termal: Paket + bakır alan ile kaybı taşıyabilme.

Öneri tablosu

| Sıra | Sınıf | Örnek aileler | Neyi iyileştirir? | Ne zaman seçilir? | Not |

|---|---|---|---|---|---|

| 1 | Ultra düşük maliyet LDO | ME6211 / XC6206 sınıfı | Çok düşük maliyet | Yük düşükse ve iyi doğrulama yapılacaksa | Lot/üretici değişkenliği için test şart |

| 2 | Mainstream modern LDO | AP2112K / TLV75x / MCP18xx sınıfı | Dengeli dropout + Iq + stabilite | Dijital 3V3 omurga | R6 için varsayılan seçim sınıfı |

| 3 | Düşük gürültü / yüksek PSRR LDO | TPS7A / ADP sınıfı | Daha temiz 3V3 | Hassas analog/ADC referansı varsa | Dijital omurgada her zaman şart değil |

| 4 | Senkron buck (3V3) | TPS62xxx / MP21xx sınıfı | Isınmayı ciddi azaltır, verim artar | 3V3 akımı büyüdüyse (500mA+) | EMI/layout disiplin ister |

Tahmini maliyet analizi (3V3 dijital omurga)

Aşağıdaki maliyetler tahmini olup tedarikçi/adet/stok/kur durumuna göre değişir. Amaç; 3V3 omurganın BOM etkisini ve alternatiflerin maliyet farkını görünür kılmaktır.

Bu maliyet tablosu yalnız 3V3 regülatör + giriş/çıkış kapasitörleri alt bloğunu kapsar.

- 5V boost (TPS61088) ayrı sayfada,

- GSM 3V8 besleme (LT1528) ayrı sayfada,

- Şarj/power‑path (BQ24298) ayrı sayfada,

- Fuel gauge (MAX17055) ayrı sayfadadır.

Varsayımlar (R6 hedef)

- Regülatör: AP2112K‑3.3TRG1 (SOT‑25)

- CIN: +

- COUT: +

- MLCC: X7R, 10V, 0805/1206 (DC‑bias marjı için)

Komponent seçimi + alternatifler (fiyat karşılaştırmalı)

| Fonksiyon | Seçenek | Paket / sınıf | Prototip (1–10) | Pilot (100) | Seri (1k+) | Not |

|---|---|---|---|---|---|---|

| 3V3 LDO (varsayılan) | AP2112K‑3.3TRG1 | SOT‑25, 600mA | $0.22 | $0.14 | $0.09 | R6 varsayılan; BOM sade |

| 3V3 LDO (termal güçlü) | AP2112R5‑3.3TRG1 | SOT‑89‑5 | $0.32 | $0.22 | $0.16 | 300mA+ sürekli akımda daha rahat |

| 3V3 LDO (termal güçlü) | AP2112M‑3.3TRG1 | SO‑8 | $0.36 | $0.25 | $0.18 | Bakır alan/ısı yayılım avantajı |

| Ucuz LDO sınıfı | ME6211‑3.3 / XC6206‑3.3 | SOT‑23 | $0.12 | $0.07 | $0.05 | Lot değişkenliği → test şart |

| Modern LDO sınıfı | TLV75533 / MCP18xx | SOT‑23‑5 | $0.35 | $0.24 | $0.17 | PSRR/kararlılık varyantına göre |

| Buck (verim odaklı) | TPS62xxx / MP21xx | QFN/SOT | $0.90 | $0.65 | $0.45 | 500mA+ akımda ısıyı düşürür, EMI zor |

Fiyatlar tedarik kanalına göre ciddi değişir.

R6 için “en iyi” seçim her zaman en ucuz olan değildir: 3V3 omurga kararsız olursa tüm sistem resetlenir ve saha maliyeti BOM’dan pahalıya gelir.

R6 hedef BOM kırılımı (AP2112K + kapasitörler)

| Kalem | Adet | Prototip (1–10) | Pilot (100) | Seri (1k+) | Not |

|---|---|---|---|---|---|

| AP2112K‑3.3TRG1 | 1 | $0.22 | $0.14 | $0.09 | SOT‑25 |

| CIN: X7R 10V | 1 | $0.09 | $0.06 | $0.04 | 0805/1206 |

| COUT: X7R 10V | 1 | $0.09 | $0.06 | $0.04 | 0805/1206 |

| CIN bypass: X7R | 1 | $0.004 | $0.002 | $0.0015 | 0402/0603 |

| COUT bypass: X7R | 1 | $0.004 | $0.002 | $0.0015 | 0402/0603 |

| TOPLAM (3V3 blok) | $0.408 | $0.264 | $0.173 | Regülatör + CIN/COUT |

Opsiyonel ekler

| Opsiyon | Adet | Prototip | Pilot | Seri | Açıklama |

|---|---|---|---|---|---|

| 3V3 omurga bulk (22–47µF ek) | 1–2 | $0.18 | $0.12 | $0.08 | Reset riski görülürse |

| TVS/ESD (3V3 hat koruma) | 1 | $0.08 | $0.06 | $0.04 | Harici konnektöre gidiyorsa |

Bu blokta maliyet düşürmek istiyorsan, önce kapasitör boyutunu/kategorisini optimize et.

Regülatörü “aşırı ucuz” sınıfa çekmek, sahada reset/kararsızlık riski doğurursa toplam maliyeti artırır.