Bu teknik doküman B107AA R6 için hazırlanmış olup yeni yapılacak olan tasarımlara kaynak niteliğindedir.

Enerji Analizör Beslemesi

Bu sayfa 2026-01-11 tarihinde güncellendi (R6 format + maliyet analizi eklendi).

Enerji analizör katmanı; şebeke tarafına bağlı yüksek gerilim ölçümleri (3 faz voltaj, akım trafoları vb.) içerdiği için hem güvenlik hem de ölçüm doğruluğu açısından güç ve sinyal katmanında izolasyon uygulanır.

Bu dokümanda R6 hedef topolojisi, R5’te sahada doğrulanmış yaklaşım referans alınarak dokümante edilmiştir:

- Güç izolasyonu: 5V → 5V_ISO (izole DC/DC)

- Regülasyon + filtreleme: 5V_ISO → 3V3_ISO (AP2112K-3.3)

- Sinyal izolasyonu: SPI/UART/interrupt hatları için dijital izolator (R5’te ISO7741 sınıfı)

R4 tecrübesinde, 3V3 → 3V3_ISO doğrudan izolasyon senaryosunda ölçüm tarafında sapmalar gözlemlenmiştir. Bu nedenle R6’da güç izolasyonu 5V seviyesinde yapılır; ardından LDO ile 3V3_ISO üretilerek izole ray “temiz” tutulur.

Topoloji

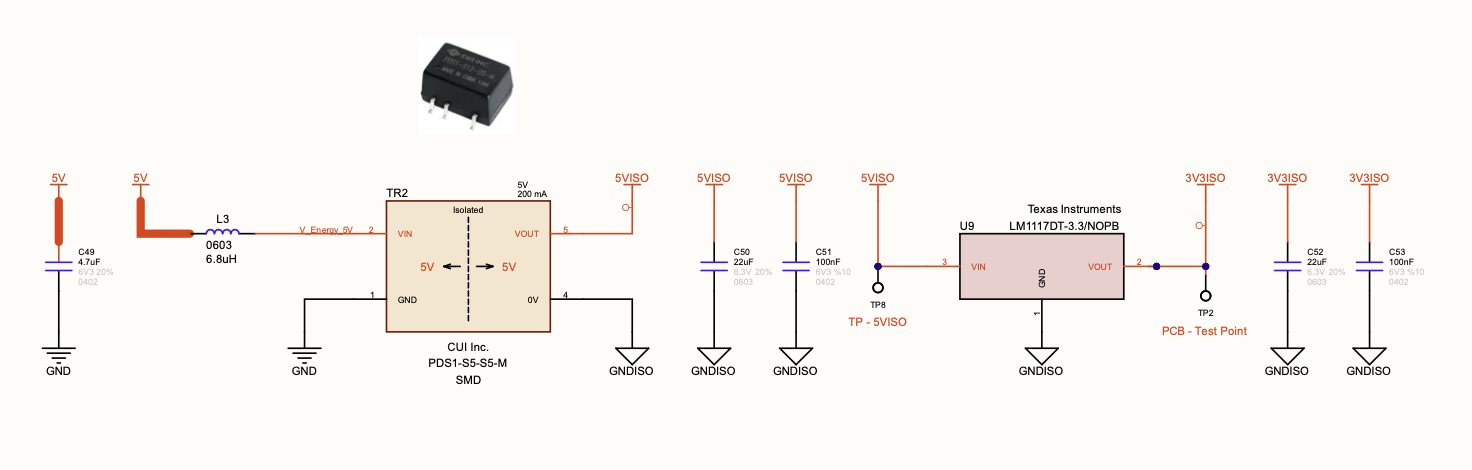

Enerji analizör beslemesinin güç yolu aşağıdaki gibidir:

- Ana 5V omurga → giriş filtresi (C49 + L3)

- İzole DC/DC:

PDS1-S5-S5-M→ 5V_ISO - İzole LDO:

AP2112K-3.3→ 3V3_ISO - İzole yükler: MAX78630 enerji ölçüm SoC + izole tarafta kalan lojikler

Şematikte kullanılan temel pasifler:

- Primary (5V): C49 = , L3 =

- Secondary (5V_ISO): C50 = , C51 =

- 3V3_ISO (AP2112K çıkışı): C52 = , C53 =

Neden 5V → 5V_ISO → 3V3_ISO

Bu topolojinin iki kritik getirisi var:

- İzole DC/DC ripple’ını LDO ile bastırma

İzole DC/DC’ler doğası gereği anahtarlama ripple’ı üretir. 5V seviyesinde izolasyon yapıp ardından LDO ile 3V3 üretmek; LDO’nun PSRR etkisiyle 3V3_ISO hattını daha sakin hale getirir.

- Yük geçişlerinde ölçüm referansını koruma

Enerji analizör SoC (ve izole taraftaki dijital hatlar) anlık akım çekişleri yaptığında, doğrudan 3V3→3V3_ISO izolasyonda bu akımlar izolasyon dönüştürücüsünün regülasyon döngüsünü daha sert zorlayabilir. 5V seviyesinde daha “sert” bir güç taşıyıp, 3V3’ü lokal LDO ile üretmek ölçüm tarafında pratikte daha stabil davranış üretir.

Akım bütçesi ve kapasite kontrolü

R6 hazırlığında amaç, izole beslemenin tasarımda güvenli marj bırakmasıdır. PDS1-S5-S5-M izole DC/DC modülü 1W sınıfındadır; 5V çıkışta teorik maksimum akım:

İzole 3V3 tarafı için pratik akım bütçesi (MAX78630 + izolator + çevre pasif/LED yok varsayımı):

- MAX78630 + osilatör + IO: (tasarım varsayımı)

- Dijital izolator (izole tarafta VCC1): (hız ve yük durumuna bağlı)

- Marj (ölçüm senaryoları / tolerans):

Bu nedenle R6 için önerilen “tasarım yük bütçesi”:

Bu bütçeyle LDO ve DC/DC’nin termal ve regülasyon davranışı rahat kalır.

R6 prototipte mutlaka doğrulama yap: 3V3_ISO hattına seri düşük değerli bir şönt ile (veya akım probu ile) gerçek akımı ölç. Eğer 50mA’nin belirgin üstüne çıkıyorsa; PDS1 seçimi, 5VISO/3V3ISO kapasitörleri ve LDO seçimi birlikte yeniden ele alınır.

Kapasitör ve endüktör mühendisliği

Primary tarafta giriş filtresi

Şematikte 5V omurgası ile izole DC/DC arasına C49 + L3 yerleştirilerek anahtarlama akımlarının omurgaya taşınması azaltılır.

Teorik kesim frekansı:

Bu değer, 100kHz–MHz bandındaki anahtarlama bileşenlerinin omurgaya kuplajını azaltmak için iyi bir “ilk mertebe” bastırma ölçeğidir.

5V_ISO dekuplajı

İzole DC/DC çıkışında iki amaç vardır:

- Bulk (C50): düşük/orta frekanslı dalgalanmayı ve yük geçişlerini sönümlemek

- HF bypass (C51): yüksek frekanslı anahtarlama bileşenlerini kısa devrelemek

Yük geçişi esnasında yalnız kapasitöre binen ani gerilim değişimi yaklaşık:

Örnek (tasarım sezgisi): ve için,

- ise:

Bu yüzden 5V_ISO tarafında bulk kapasitörün DC/DC’ye yakın olması ve layout’un sıkı tutulması önemlidir.

3V3_ISO bulk kapasitörü

3V3_ISO hattında bulk kapasitör, ölçüm SoC’un (MAX78630) ani akım değişimlerinde hattı stabil tutar. Aynı örnek ile (30mA, 10µs):

Yani seviyesinde bir droop beklenir; bu ölçüm doğruluğu açısından çok daha “konforlu” bir seviyedir.

AP2112K, düşük ESR’li seramik kapasitörlerle stabil çalışacak şekilde tasarlanmıştır; bu nedenle LM1117’deki gibi “ESR aralığı” şartı beklenmez.

Buna rağmen validasyonda 3V3_ISO hattında osilasyon/ripple görülürse önce şunları kontrol et:

- C52/C53’ün regülatöre fiziksel yakınlığı (loop alanı büyüdüyse ripple artar)

- C52’nin efektif kapasitansı (MLCC DC-bias ile düşer; 22µF seçimi bu yüzden avantajlıdır)

- GNDISO dönüş yolu (izole tarafta uzun/ince hatlar transient’i büyütür)

AP2112K için pratik minimum kural: giriş ve çıkışta en az seramik kapasitör mutlaka bulunmalı; bulk kapasite (22µF gibi) yük transient’lerini iyileştirir.

Termal değerlendirme

LDO kaybı

AP2112K için güç kaybı:

Örnek:

→

→

Bu seviyeler, yeterli bakır alan ile tipik olarak problem yaratmaz.

AP2112K’nin dropout gerilimi yüke bağlıdır; ancak bu tasarımda izole 3V3 hattı düşük akım (tasarım bütçesi ) çektiği için 5V_ISO → 3V3_ISO dönüşümünde regülasyondan çıkma riski pratikte yoktur.

İzole DC/DC kaybı

PDS1 tarafında kayıp, verime bağlıdır. İzole güçte genel kural: yük arttıkça verim artar, çok hafif yükte verim düşebilir. R6’da 50mA bütçesi ile (5VISO tarafında yaklaşık 30–60mA mertebesi) modül rahat kalır.

Komponent seçimi

R5 referansı ile uyumlu olacak şekilde R6’da önerilen seçimler:

- TR2 – İzole DC/DC:

PDS1-S5-S5-M(CUI Inc., 5V→5V, 1W sınıfı) - U9 – İzole LDO:

AP2112K-3.3(Diodes Inc.) veya muadili

Pasifler (şematik değerleri + PN önerisi):

- L3 – (0603):

- Öneri:

Murata LQM18FN6R8M70L - Alternatif:

TDK MLZ1608M6R8WT000

- Öneri:

- C49 – (0402): X7R,

- Öneri:

Murata GRM155R71A475KE15

- Öneri:

- C50 – (0603): X7R,

- Öneri:

Murata GRM188R71A225KE15

- Öneri:

- C51/C53 – (0402): X7R,

- C52 – (0603): mümkünse 10V (tercihen 16V) sınıfına çık; MLCC DC-bias düşümüne karşı marj sağlar

R5’te 5V seviyesinde 6.3V MLCC kullanılmıştı. 5V hatlarda MLCC derating etkileri nedeniyle R6’da 10V (tercihen 16V) sınıfına çıkmak daha stabil bir gerçek kapasitans sağlar.

İzole dekuplaj

İzole 3V3 rayının “temiz” kalması için yüklerin kendi pinlerinde dekuplajı kritik önemdedir. R5 şematiğinde görülen yaklaşım:

- MAX78630 besleme pinleri: 3V3_ISO’dan R54 = 0Ω üzerinden V3P3A/V3P3D hatlarına dağıtım yapılır; her iki hatta C62/C63 = 100nF ile yakın dekuplaj uygulanır.

- ISO7741 sınıfı dijital izolator: VCC1 (izole taraf) üzerinde C54 = 100nF ile yakın dekuplaj uygulanır.

Bu yöntem; dijital geçişlerin ve anahtarlama parazitlerinin ölçüm referansına taşınmasını azaltır.

PCB yerleşim ve izolasyon kuralları

Bu raylar tamamen izole olduğundan, layout’ta temel kurallar:

- GND ↔ GNDISO kesin ayrılmalı; bariyeri bakır dolgu ile “köprüleme”.

- İzolasyon bariyerinde via/copper/TP ile yanlışlıkla bağlantı oluşturma.

- İzole DC/DC ve izole LDO çevresindeki akım döngülerini küçük alanlı tut.

- 100nF dekuplajları ilgili IC pinlerine en yakın yerleştir.

- Creepage/clearance’ı saha gerilim seviyelerine göre tasarla; gerekiyorsa bariyerde slot kullan.

Ölçüm ve doğrulama

- TP8 (TP_5VISO):

- TP2 (PCB - Test Point / 3V3ISO):

Validasyon adımları:

- Adaptörle sistem çalışırken TP8 ve TP2 ölç.

- Enerji analizör aktif ölçüm modunda iken 3V3_ISO ripple’ı osiloskopla gözle.

- SPI/UART trafiği yoğunken 3V3_ISO hattında ek parazit oluşuyor mu kontrol et.

- Kutu içi senaryoda (ısı artışı) LDO sıcaklığını kontrol et.

Tahmini maliyet analizi (Enerji analizör izole besleme bloğu)

Aşağıdaki maliyetler tahmini olup tedarikçi/adet/stok/kur durumuna göre değişir. Bu tablo yalnızca enerji analizörün izole besleme alt bloğunu kapsar:

- 5V omurga giriş filtresi (C49+L3)

- İzole DC/DC (5V→5V_ISO)

- İzole LDO (5V_ISO→3V3_ISO)

- İzole taraftaki temel dekuplajlar

Bu tabloda MAX78630, kristal, dijital izolator (ISO7741 sınıfı) ve ölçüm giriş katmanı pasifleri dahil değildir.

Amaç: yalnızca “izole güç üretimi”nin BOM etkisini net görmek.

R6 hedef BOM kırılımı

| Kalem | Adet | Prototip (1–10) | Pilot (100) | Seri (1k+) | Not |

|---|---|---|---|---|---|

| İzole DC/DC: PDS1‑S5‑S5‑M (1W) | 1 | $4.60 | $3.40 | $2.80 | 5V→5V_ISO |

| LDO: AP2112K‑3.3 | 1 | $0.22 | $0.14 | $0.09 | 5V_ISO→3V3_ISO |

| L3: 6.8µH (Murata LQM18FN6R8M70L) | 1 | $0.18 | $0.12 | $0.08 | Primary filtre |

| C49: 4.7µF X7R ≥10V (0402) | 1 | $0.06 | $0.04 | $0.03 | DC-bias marjı |

| C50: 2.2µF X7R ≥10V (0603) | 1 | $0.04 | $0.025 | $0.018 | 5V_ISO bulk |

| C51: 100nF X7R ≥10V (0402) | 1 | $0.004 | $0.002 | $0.0015 | 5V_ISO HF |

| C52: 22µF X7R 10V/16V (0603) | 1 | $0.12 | $0.08 | $0.055 | 3V3_ISO bulk |

| C53: 100nF X7R ≥10V (0402) | 1 | $0.004 | $0.002 | $0.0015 | 3V3_ISO HF |

| TOPLAM (izole besleme bloğu) | $5.228 | $3.809 | $3.076 | Opsiyonelsiz |

Opsiyonel iyileştirmeler (saha riskine göre)

| Opsiyon | Adet | Prototip | Pilot | Seri | Ne zaman? |

|---|---|---|---|---|---|

| 3V3_ISO ek bulk (22–47µF) | 1–2 | $0.12–0.24 | $0.08–0.16 | $0.055–0.11 | Ripple/transient görülürse |

| 5V_ISO ek bulk (4.7–10µF) | 1 | $0.06 | $0.04 | $0.03 | DC/DC çıkış droop’u varsa |

Komponent seçimi ve alternatifler (fiyat karşılaştırmalı)

İzole DC/DC modülü

| Seçenek | Sınıf | Prototip | Pilot | Seri | Not |

|---|---|---|---|---|---|

| PDS1‑S5‑S5‑M | 1W | $4.60 | $3.40 | $2.80 | R5 referansı ile uyumlu |

| Recom Rxx‑0505S sınıfı | 1W | $3.90 | $2.90 | $2.40 | Tedarik alternatif |

| 2W sınıfı izole DC/DC | 2W | $6.50 | $4.80 | $4.00 | Eğer akım bütçesi büyürse |

Burada “daha ucuz” tercihler genelde iki risk getirir:

- Daha yüksek ripple / daha zayıf transient davranışı

- Daha tutarsız verim (özellikle hafif yükte)

R6 yaklaşımı: önce ölçüm doğruluğu ve stabilite, sonra maliyet optimizasyonu.

3V3_ISO regülatör

| Seçenek | Paket | Prototip | Pilot | Seri | Not |

|---|---|---|---|---|---|

| AP2112K‑3.3 | SOT‑25 | $0.22 | $0.14 | $0.09 | BOM sade, yeterli |

| AP2112R5‑3.3 | SOT‑89‑5 | $0.32 | $0.22 | $0.16 | Termal daha rahat |

| TLV75533 sınıfı | SOT‑23‑5 | $0.35 | $0.24 | $0.17 | PSRR/kararlılık varyantına göre |

Toplam maliyet özeti (R6)

-

İzole besleme bloğu (minimum):

- Prototip: $5.228

- Pilot: $3.809

- Seri: $3.076

-

Opsiyonel bulk’lar dahil (maksimum tipik):

- Prototip: 5.8

- Pilot: 4.2

- Seri: 3.4

Bu blokta maliyet kırmanın “en pahalı” sonucu genelde şudur:

- 3V3_ISO ripple/dip → ölçüm sapması / hatalı enerji ölçümü

Bu yüzden R6’da önce osiloskop ölçümüyle 3V3_ISO davranışı doğrulanır; gerekiyorsa kapasitör sınıfı (10V/16V) ve bulk değerleri revize edilir.