Bu teknik doküman B107AA R6 için hazırlanmış olup yeni yapılacak olan tasarımlara kaynak niteliğindedir.

FOTA Modülü Güç Kontrolü

Bu sayfa 2026-01-11 tarihinde güncellendi (R6 format + hesaplar + maliyet analizi eklendi).

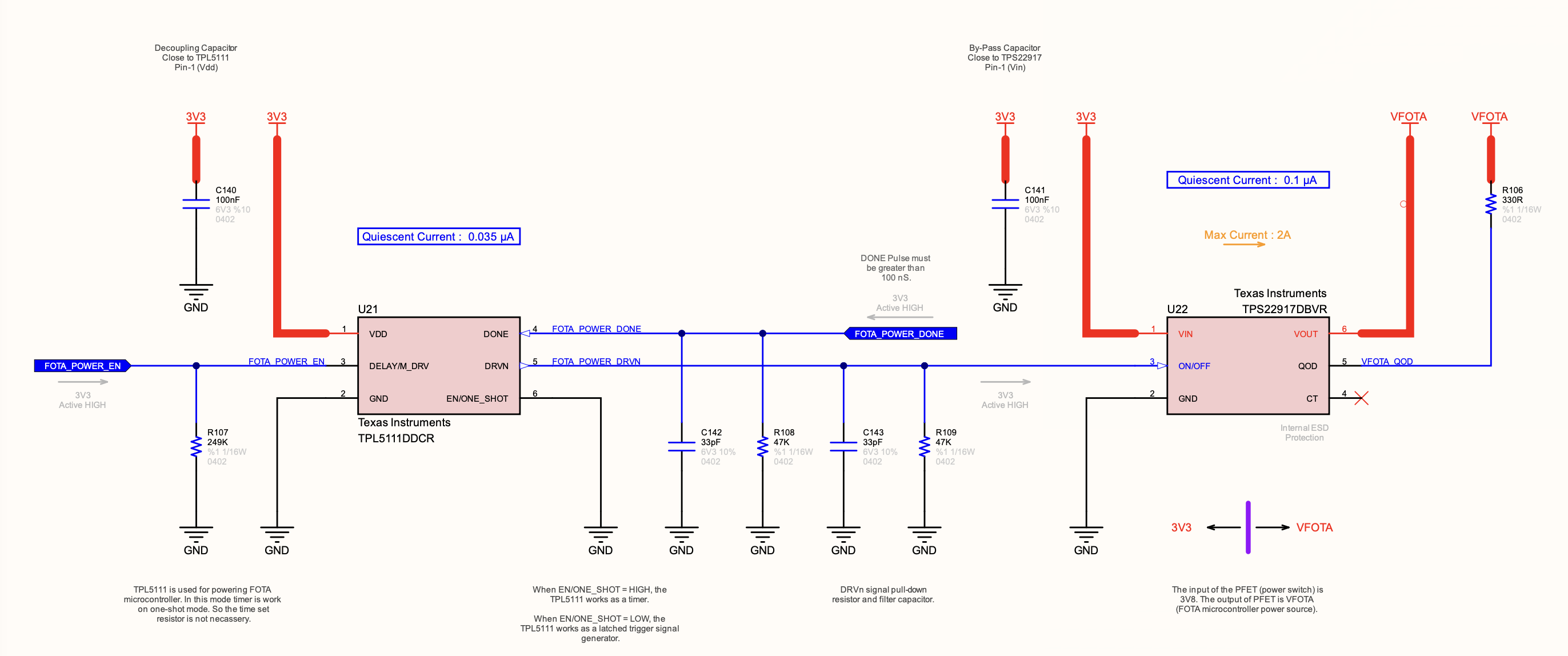

FOTA katmanı (FOTA MCU + FOTA LED’leri + FOTA burn buffer), ana sistemden bağımsız olarak açılıp kapanabilen ayrı bir güç domaini olacak şekilde tasarlanmıştır. Bu domainin besleme hattı VFOTA olarak adlandırılır ve 3V3 omurgasından türetilir.

Bu sayfadaki amaç; VFOTA’nın nasıl açılıp kapandığını, kullanılan bileşenlerin neden seçildiğini ve sahada güvenilir çalışması için kritik mühendislik noktalarını netleştirmektir.

Topoloji

VFOTA güç kontrolü iki bloktan oluşur:

- U21 (latched trigger / timer): MCU’dan gelen tetik ile VFOTA’yı açtırır, FOTA MCU’dan gelen

DONEdarbesi ile kapatır. - U22 (load switch): 3V3’ü VFOTA hattına taşır. Açma-kapama davranışı, kontrollü açılış (slew rate / soft-start) ve hızlı boşaltma (quick output discharge) gibi güç kalitesi konularını yönetir.

Bu yaklaşımın ana kazancı: Ana sistem 7/24 açık kalırken, FOTA katmanı yalnız gerektiğinde açılır ve iş bitince donanım seviyesinde kapanır.

Kullanılan bileşenler ve seçim gerekçeleri

| Blok | Ref | Bileşen | Neden bu bileşen? |

|---|---|---|---|

| Latched trigger | U21 | TPL5111DDCR | Ultra düşük bekleme tüketimi (nA seviyesinde), DONE darbesi ile donanım tabanlı kapanış, M_DRV ile manuel/harici tetik desteği. |

| Yük anahtarı | U22 | TPS22917DBVR | 1–5.5V aralığı, 2A sınıfı, düşük , CT ile ayarlanabilir slew rate, QOD ile kontrollü deşarj, reverse-current blocking. |

Bu topoloji “MCU bir pin kaldırdı → güç açıldı, başka bir pin kaldırdı → güç kapandı” gibi basit bir yaklaşım değildir.

Kapanış mekanizmasının DONE darbesi ile donanımda tanımlı olması, firmware kaynaklı “unutma” veya kilitlenme senaryolarında riski azaltır.

Sinyaller ve varsayılan durum

FOTA_POWER_EN: Ana MCU’nun tetik sinyalidir.FOTA_POWER_DRVN: U21’in ürettiği sürücü çıkışıdır; U22’ninONpinini sürer.FOTA_POWER_DONE: FOTA MCU’nun ürettiği DONE darbesidir.

Varsayılan durumda (reset / güç verildiği an):

FOTA_POWER_EN = LOWFOTA_POWER_DRVN = LOW→ U22 kapalı- VFOTA kapalıdır ve QOD konfigürasyonuna göre VFOTA hattı kontrollü şekilde boşaltılır.

Çalışma mantığı

Kritik zamanlama gereksinimleri

Bu blokta iki zamanlama kritik:

- DONE darbesi (FOTA MCU → TPL5111)

- Manuel tetik darbesi (harici/debug tetik → DELAY/M_DRV)

DONE darbesi (FOTA_POWER_DONE)

TPL5111, DONE pininde LOW→HIGH geçişini “geçerli tamamlandı” olarak algılar.

Datasheet’e göre minimum DONE darbe genişliği:

Pratikte firmware tarafında bunu “tam sınırda” üretmek yerine, gürültü/kenar yumuşatma ihtimallerini de düşünerek:

- 1–5 ms aralığında bir

DONEpulse üretmek güvenli bir mühendislik tercihidir.

Not: TPL5111 aynı interval içinde birden fazla

DONEgörürse yalnız ilkini işler.

Manuel tetik (DELAY/M_DRV)

DELAY/M_DRV pinine uygulanan “manuel power-on” darbesinin datasheet’te tanımlı gözlem penceresini aşması gerekir. Pratik kural:

Bu yüzden harici debug/elektrikçi aparatı ile tetik verilecekse, tetik darbesi en az 20ms olacak şekilde tasarlanmalıdır.

Fail-safe kapanış (DONE gelmezse)

FOTA MCU kilitlenip DONE üretmezse, TPL5111 programlanan aralık sonunda DRVn’i de-assert eder ve VFOTA kapanır.

Bu fail-safe davranışın garantili olabilmesi için REXT datasheet aralığında seçilmelidir.

TPS22917 Güç kalitesi

Inrush akımı

VFOTA açıldığında en büyük risk, VFOTA hattındaki toplam kapasitansın bir anda şarj olması nedeniyle oluşan inrush akımıdır. Basit model:

Burada VFOTA hattındaki toplam efektif kapasitans (kondansatörler + modül giriş kapasiteleri), ise U22’nin çıkış ramp hızıdır.

TPS22917’de ramp hızı CT pini ile yavaşlatılabilir. Böylece:

- 3V3 hattında çökme (dip) riski azalır,

- reset / brown-out ihtimali düşer,

- EMI ve kablo/hat rezonansları daha az tetiklenir.

Soft start

TPS22917’de CT pini, VOUT yükseliş eğimini kontrol ederek inrush akımını yönetmemize izin verir.

Inrush basit yaklaşım:

Burada VFOTA üzerindeki toplam efektif kapasitans, ise VOUT ramp hızıdır.

Hedefleme yöntemi (R6)

- VFOTA hattının efektif kapasitansını belirle:

- 3V3 omurgayı çökertmeyecek bir inrush limiti seç:

- Buna göre hedef ramp hızını bul:

- CT’yi TPS22917 datasheet yaklaşımıyla seç:

TPS22917 için uygulama notlarında verilen örnekten hareketle alınabilir.

Örnek hesap (pratik ve hızlı)

- Eğer ve hedeflenirse:

Bu durumda E12 seçim:

-

680 pF (C0G/NP0 tercih) iyi bir başlangıçtır.

-

Eğer ise aynı limitte:

Bu durumda:

- 330 pF – 470 pF iyi bir başlangıçtır.

CT’nin tek “doğru” değeri yoktur.

R6 doğrulama akışı:

- VFOTA açılışında 3V3 dip var mı?

- VFOTA ramp eğrisi beklenenden hızlı mı?

Sorun görülürse CT artırılarak ramp yavaşlatılır (inrush düşer).

QOD ile kontrollü kapanış

TPS22917’nin QOD fonksiyonu, kapanışta VFOTA hattını “floating” bırakmak yerine kontrollü şekilde boşaltmak için kullanılır.

Datasheet’e göre QOD yolu için iç deşarj direnci mevcuttur ve dışarıdan ek direnç ile düşüş süresi ayarlanabilir. Pratik model:

- QOD doğrudan VOUT’a bağlıysa: (hızlı deşarj)

- QOD–VOUT arasına direnç eklenirse: (daha yavaş)

Yaklaşık düşüş süresi:

Örnek (hızlı kapanış)

- Varsayım:

- İç deşarj: mertebesi

Bu yaklaşımın faydası: VFOTA kapanınca hat kısa sürede 0V’a yaklaşır ve “yarım besleme / brown bölgesi” senaryoları azalır.

Eğer VFOTA hattı çok büyük kapasitans taşıyorsa veya kapanış sırasının kontrollü uzatılması gerekiyorsa QOD–VOUT arasına harici direnç eklenerek düşüş uzatılabilir.

Güç kaybı ve termal değerlendirme

TPS22917 bir LDO gibi “(Vin–Vout)×I” kaybı oluşturmaz; kayıp büyük ölçüde iletim direncine bağlıdır:

Örnek (temsilî):

Bu değer çok düşüktür; dolayısıyla bu blokta ana risk ısınma değil, inrush ve güç bütünlüğüdür.

PCB yerleşim

- U22’nin VIN/VOUT/GND döngüsü mümkün olduğunca kısa ve geniş olmalı.

- U22 girişine yakın bir CIN (en az 1µF + 100nF) mutlaka yerleştirilmeli; 3V3 kaynağı “yavaş” ise ek bulk gerekebilir.

- CT kondansatörü kullanılacaksa U22’ye çok yakın konumlandırılmalı.

- QOD hattı, VOUT’a giden deşarj yoludur; gereksiz uzun hatlardan kaçın.

FOTA_POWER_ENveFOTA_POWER_DONEhatları dijital sinyaldir; ancak VFOTA anahtarlama anlarında gürültü kapabilir. Bu hatların GND referansı temiz olmalı, gerekiyorsa seri küçük direnç (22–100Ω) ile kenar yumuşatılabilir.

Doğrulama / test

- VFOTA kapalıyken: VFOTA hattının kapanıştan sonra makul sürede 0V’a yaklaştığı doğrulanır (QOD davranışı).

- VFOTA açılışında: 3V3 hattında çökme/dip var mı osiloskopla gözlenir.

- DONE senaryosu: FOTA MCU

DONEpulse ürettiğinde VFOTA’nın deterministik kapandığı doğrulanır. - DONE yok senaryosu (fail-safe): FOTA MCU bilinçli olarak

DONEüretmeyecek şekilde test edilip VFOTA’nın maksimum açık kalma süresi ölçülür (REXT ile belirlenen süre).

Bu fail-safe davranışın gerçekten devreye girebilmesi için U21’in DELAY/M_DRV pinindeki REXT değeri datasheet aralığında seçilmelidir.

- REXT aralığı: (önerilen)

- Hassasiyet: en az %1

REXT yalnız “maksimum açık kalma süresini” belirlemez; aynı zamanda start-up’ta yapılan dijital ölçümün kararlı okunması için de sınırlandırılmıştır.

Bu güç kapısı doğru çalıştığında, FOTA katmanı kilitlenirse dahi VFOTA’nın süreli açık kalıp kapanması, batarya tüketimini sınırlayan önemli bir korumadır.

Komponent seçimi ve alternatifler

VFOTA güç kapısı iki kritik entegre ve birkaç pasif ile çözülür. Bu blok “az parçayla çok iş” yapar; bu yüzden seçim kriteri yalnız fiyat değil, fail-safe davranış ve güç bütünlüğüdür.

| Blok | Ref | Seçilen (R6) | Alternatifler | Seçim notu |

|---|---|---|---|---|

| Nano timer / güç kapılama | U21 | TPL5111DDCR | TPL5110 (benzer aile), TPL5010 (watchdog’lu), MCU ile soft-timer | TPL5111: DONE ile deterministik kapanış + çok düşük bekleme |

| Load switch | U22 | TPS22917DBVR | TPS22910A/TPS22918 sınıfı load switch’ler, muadil vendor load switch | CT ile ramp kontrol + QOD ile kapanış + RCB |

| CT (soft-start) | C_T | 680 pF C0G/NP0 | 470 pF / 1 nF (C0G) | CL ve inrush hedefiyle ayarlanır |

| QOD direnç | R_QOD | DNP (varsayılan) | 330Ω–2.2kΩ | Kapanış süresi istenirse uzatılır |

| EN/DONE hat seri R | R_SIG | 22–100Ω (ops.) | 0Ω / 47Ω | Kenar yumuşatma / EMI |

Tahmini maliyet analizi (VFOTA güç kapısı)

Aşağıdaki maliyetler tahmini olup tedarikçi/adet/stok/kur durumuna göre değişir. Bu tablo yalnızca VFOTA güç kapısı (U21+U22+pasifler) içindir; FOTA MCU, LED’ler ve burn buffer bu sayfaya dahil değildir.

| Kalem | Adet | Prototip (1–10) | Pilot (100) | Seri (1k+) | Not |

|---|---|---|---|---|---|

| TPL5111DDCR | 1 | $0.65 | $0.42 | $0.32 | Nano timer |

| TPS22917DBVR | 1 | $0.38 | $0.25 | $0.18 | Load switch |

| CT (680 pF C0G) | 1 | $0.03 | $0.015 | $0.01 | 0603/0402 |

| CIN (1–10 µF) + 100 nF | 2 | $0.10 | $0.06 | $0.04 | Regülasyon/decouple |

| QOD ops. direnç + sinyal seri R | 2 | $0.004 | $0.002 | $0.0014 | Opsiyonel |

| TOPLAM (VFOTA güç kapısı) | $1.164 | $0.747 | $0.551 | Opsiyonelsiz/az opsiyonlu |

Bu blokta maliyet kırmanın “en pahalı” sonucu genelde şudur: VFOTA açılışında 3V3 dip → ana MCU reset → FOTA akışı bozulur.

Bu yüzden R6 yaklaşımı: önce güç bütünlüğünü garanti et, sonra gerekiyorsa CT/QOD ile ince ayar yap.