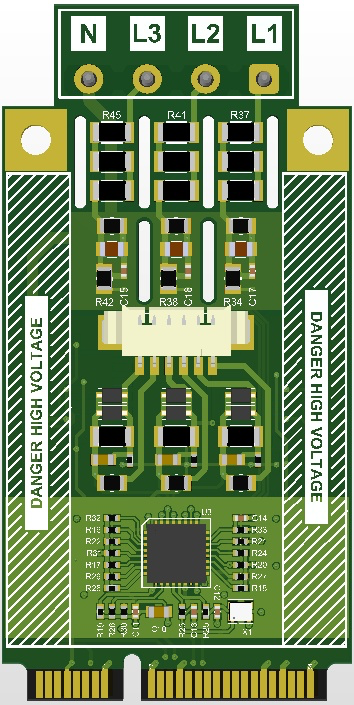

B202AA-PCIe

B202AA-PCIe is an open-source module I developed to securely collect three-phase energy data from the field and transfer it to the host system. The design approach is to consolidate the measurement side on a single board and reduce the integration load on the main system board. In this way, both the development process becomes simpler and a more predictable structure is achieved in field installations.

In Mini PCIe Form

This product uses the Mini PCIe form not to be an electrical PCIe peripheral card, but to provide a mechanical standard and easy integration. In practice, this approach enables the use of a common module across different carrier boards and makes the system architecture more modular. The main purpose of the board is to manage energy measurement internally and present a simpler interface layer to the outside world.

What It Is Not

B202AA-PCIe is not an expansion card that works over PCIe lanes in the classical sense. This module is positioned as an independent measurement block that performs three-phase measurement and exposes the result through isolated communication. Keeping this distinction clear is important for correctly managing expectations and design decisions during integration.

What It Solves

In three-phase systems, the main challenge is not only taking measurements, but also safely managing the high-voltage area while keeping the host side clean and serviceable. B202AA-PCIe is designed by separating these two worlds; the field measurement layer operates in its own domain, while the host side sees an isolated interface. This allows product development teams to move forward on a reusable foundation instead of rebuilding the measurement infrastructure from scratch in every project.

What Can It Measure?

The energy analyzer has measurement sets that may vary depending on the usage scenario.

| Parameter | Short description |

|---|---|

| Instantaneous Voltage | Instantaneous voltage value for all phases (phase-to-neutral). |

| RMS Voltage | RMS voltage value for all phases. |

| RMS Voltage average | Average RMS voltage of all phases. |

| Fundamental Voltage | Fundamental frequency (1st harmonic) voltage component for all phases. |

| Harmonic Voltage | Total voltage effect of harmonic components for all phases. |

| Instantaneous Current | Instantaneous current value for all phases. |

| Peak Current | Peak current value for all phases. |

| RMS Current | RMS current value for all phases. |

| RMS Current average | Average RMS current of all phases. |

| Fundamental Current | Fundamental frequency (1st harmonic) current component for all phases. |

| Harmonic Current | Total current effect of harmonic components for all phases. |

| Fundamental Reactive Power | Reactive power at fundamental frequency (Q1) for all phases. |

| Harmonic Reactive Power | Reactive power caused by harmonics (Qh) for all phases. |

| Active Power | Active power (P) for all phases. |

| Reactive Power | Reactive power (Q) for all phases. |

| Apparent Power | Apparent power (S) for all phases. |

| Active Power average | Average active power of all phases. |

| Reactive Power average | Average reactive power of all phases. |

| Apparent Power average | Average apparent power of all phases. |

| Fundamental Power | Power component at fundamental frequency (P1/S1) for all phases. |

| Harmonic Power | Power caused by harmonic components (Ph) for all phases. |

| Fundamental Volt Amperes | Apparent power at fundamental frequency (S1, VA) for all phases. |

| Power Factor | Total power factor (PF) for all phases. |

| Received Active Energy | Total imported active energy drawn from the grid. |

| Delivered Active Energy | Total exported active energy delivered to the grid. |

| Reactive Energy Leading | Total capacitive (leading) reactive energy for all phases. |

| Reactive Energy Lagging | Total inductive (lagging) reactive energy for all phases. |

| Frequency | Grid frequency (Hz). |

Typical Use Cases

The module can be comfortably used in energy monitoring infrastructures, industrial panel tracking, agricultural energy analysis, and remote monitoring setups. The common need is to transfer three-phase information to upper-level software in a regular and secure way. B202AA-PCIe addresses this need by combining data collection and alarm monitoring in the same integration line.

Integration Logic

On the host side, the setup follows a simple flow: the module is powered, the power enable line is controlled, and then measurement and status data are received via UART communication. This arrangement reduces startup instabilities frequently seen in the field and makes system behavior more predictable. Presenting alarm and phase monitoring lines on the same module also improves situation awareness on the upper system side.

Safety Note

This module is used in applications that include mains-level high voltage. Installation, testing, and maintenance steps must be carried out only by qualified personnel, with appropriate isolation, enclosure, and field safety standards in place.

Downloadable Resources

You can review all design files, schematics, and manufacturing outputs in the Github B202AA-PCIe repository.

Bu kütüphane, gerçek sahada kullanılan projelerden gelen ihtiyaçlara göre sürekli gelişen bir açık kaynak projedir. Kullanıcı geri bildirimleri, yeni fonksiyonların eklenmesi ve mevcut yapının iyileştirilmesi açısından kritik öneme sahiptir.

Bu kütüphaneyi hem kişisel hem de ticari projelerinde özgürce kullanabilirsin. Herhangi bir lisans kısıtı uygulanmamaktadır; amacım, bu kütüphanenin mümkün olduğunca fazla gerçek dünya projesinde yer almasıdır. Özel bir entegrasyon ihtiyacın, ticari bir planın veya teknik bir sorunun varsa bana e‑posta üzerinden her zaman ulaşabilirsin: akkoyun@me.com Geri bildirimlerini veya kullanım senaryolarını paylaşman, projeyi geliştirmem açısından büyük katkı sağlar.