Reset / Boot Davranışı

Bu sayfa, B107AA R6 ana işlemcisinin reset kaynaklarını, watchdog (WDT) topolojisini ve reset sonrası sistemin güvenli moda nasıl geçtiğini tanımlar. Sahadaki motor kumanda panosu koşullarında (EMI, gerilim dalgalanması, modem kilitlenmeleri) reset stratejisi “nadiren reset”ten çok, öngörülebilir şekilde toparlanma hedefiyle ele alınır.

Reset kaynakları

ATmega2560 tarafında reset, birden fazla kaynaktan tetiklenebilir. Bu kaynakların her biri farklı bir arıza sınıfına karşı koruma sağlar.

POR (Power-On Reset)

3V3 hattı ilk kez yükselirken MCU, POR ile deterministik bir başlangıç yapar. Bu reset türünde amaç; IO pinlerinin bilinmeyen bir durumda kalmasını engellemek ve boot akışının her açılışta aynı şekilde başlamasını sağlamaktır.

BOR (Brown-Out Reset)

Besleme gerilimi düşerken MCU’nun “belirsiz bölgede” çalışması; flash/EEPROM yazım hataları, seri haberleşme hataları ve yanlış çıkış sürüşleri gibi sonuçlar doğurabilir. Bu nedenle BOR aktif kullanılır.

- 3.3V sistemlerde pratik yaklaşım, BOR seviyesini 2.7V bandında seçmektir.

- Nihai BOR seçimi; MCU datasheet’teki frekans–gerilim çalışma aralığı ve 3V3 regülatör davranışı ile birlikte doğrulanmalıdır.

Dahili WDT (MCU watchdog)

ATmega2560’ın dahili watchdog’u yazılım seviyesinde ek bir güvenlik katmanı olarak kullanılabilir. Dahili WDT, özellikle “ana loop çalışıyor ama belirli bir alt görev kilitleniyor” gibi senaryolarda hızlı toparlanma sağlar.

Not: Bu projede asıl “hard-lockup” toparlanması harici supervisor ile hedeflenir. Dahili WDT, firmware disiplinine bağlı bir ikinci katman olarak ele alınmalıdır.

Harici reset (kullanıcı reset butonu)

Ana işlemci reset hattı kutu dışına alınmıştır. Böylece saha personeli, cihazın kilitlendiği veya modem bağlantısının toparlanmadığı durumlarda manuel reset uygulayabilir.

Bu buton; servis/bakım senaryolarında hızlı müdahale imkânı sağlar, ancak sistem tasarımı “butona ihtiyaç duymayacak kadar” dayanıklı olmayı hedefler.

Harici watchdog / supervisor reset (MAX6369)

Sistemde MCU kilitlenmelerine karşı harici watchdog supervisor kullanılır. Bu katman, MCU tamamen cevap veremeyecek hale geldiğinde bile reset üreterek sistemi toparlar.

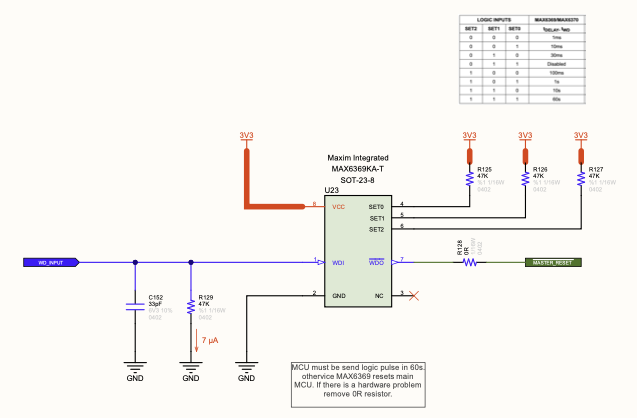

Harici watchdog devresi (MAX6369KA‑T)

R6 tasarımında MCU kilitlenmelerine karşı harici watchdog supervisor kullanılır. Buradaki hedef, MCU’nun dahili watchdog’una bel bağlamak değil; MCU veya yazılım tamamen cevap veremez hale gelse bile bağımsız bir entegre ile reset üreterek sistemi deterministik başlangıca döndürmektir.

Seçilen entegre: MAX6369KA‑T (SOT‑23‑8).

Çalışma prensibi ve sinyal akışı

MAX6369, WDI pininde belirli bir zaman penceresi içinde en az bir adet geçerli lojik geçiş (transition) görmeyi bekler. Bu geçiş gelirse zamanlayıcı sıfırlanır ve WDO pasif kalır. Geçiş gelmezse watchdog timeout olur ve WDO çıkışı aktif‑low bir reset darbesi üretir.

Bu kartta:

- WDI (Watchdog Input): MCU tarafından sürülür (periyodik toggle).

- WDO (Watchdog Output): timeout olduğunda düşük darbe üretir.

- MASTER_RESET: kartın reset omurgasıdır.

- R128 = 0R: WDO → MASTER_RESET bağlantısını “servis için sökülebilir” bir link olarak sağlar.

WDO çıkışı open‑drain tipindedir. Bu nedenle MASTER_RESET hattında harici bir pull‑up (tipik 10k civarı) bulunması önerilir; yalnızca dahili pull‑up’a bırakmak, yükselme zamanını ve gürültü bağışıklığını sahada zayıflatabilir.

Zamanlama seçimi (SET0/SET1/SET2) ve 60 saniye kararı

MAX6369 ailesinde startup delay ve watchdog timeout değerleri SET0/SET1/SET2 pinlerinin lojik durumuyla seçilir. MAX6369 için kritik bilgi: ile birbirine eşittir (aynı seçimle birlikte değişir).

Mevcut şematikte:

- R125/R126/R127 = 47k ile SET0/SET1/SET2 pinleri 3V3’e çekilidir → SET2=1, SET1=1, SET0=1.

Bu seçim, MAX6369 için minimum değer olarak:

(watchdog’un “izlemeye başlamadan önce” beklediği süre)

(normal işletimde WDI transition gelmezse timeout süresi)

Anlamı:

- Kart ilk açıldığında watchdog ilk 60 saniye boyunca WDI geçişlerini “kritik” saymaz; MCU/GSM boot sürecine zaman tanır.

- 60 saniye sonrası watchdog aktif izlemeye geçer ve MCU’nun en geç her 60 saniyede bir WDI transition üretmesini bekler.

Neden 60 saniye?

- GSM modem ayağa kalkışı, şebeke toparlanması, SIM/network gecikmeleri gibi süreçlerde “yanlış reset döngüsü” riskini azaltır.

- MCU gerçekten takıldığında sahada 60 saniye içinde toparlanma sağlar.

Firmware tarafı: WDI besleme (kick) kurgusu

MAX6369, WDI’da toggle/transition bekler; sabit seviyede kalma “besleme” sayılmaz. Bu nedenle firmware’de WDI üretimi şu prensiple ele alınmalıdır:

Pratik öneri:

- WDI toggling’i sistem sağlıklı ana döngüye girdikten sonra başlat.

- Körü körüne sabit aralıkla toggle etmek yerine, kritik alt görevlerin (örn. ölçüm okundu + paket hazırlandı + modem yanıt verdi) tamamlanmasına bağla.

Bu yaklaşım, örneğin bir fonksiyon sonsuz döngüde takılırsa WDI’nin de doğal olarak durmasını sağlar ve watchdog reset devreye girer.

WDI hattı RC ağı: filtreleme ve hesap

WDI hattında EMI kaynaklı yanlış tetiklemeleri yumuşatmak ve pinin boot sırasında “havada kalmasını” önlemek için küçük bir RC ağı bulunur:

- R129 = 47k (WDI → GND)

- C152 = 33 pF (WDI → GND)

Zaman sabiti:

Yaklaşık kesim frekansı:

Bu değer; saniyeler mertebesindeki WDI toggle’larını etkilemez, ancak çok yüksek frekanslı sivri parazitleri bir miktar yumuşatır. Buradaki amaç “darbeyi büyütmek” değil; WDI’nin default seviyesini belirlemek ve EMI’yi hafifletmektir.

WDO darbesi ve reset entegrasyonu

MAX6369 timeout olduğunda WDO’yu düşük darbe olarak üretir. Bu cihaz varyantında WDO:

- Active‑low

- Open‑drain

- Darbe genişliği: tWDO ≈ 100 ms

100 ms’lik darbe, MCU resetinin güvenli tetiklenmesi için geniş bir penceredir. WDO open‑drain olduğundan MASTER_RESET üzerindeki pull‑up ve reset hattı RC’si (varsa) birlikte değerlendirilmelidir.

Servis/üretim notu:

- WDO çıkışı R128=0R üzerinden MASTER_RESET’e bağlıdır.

- Test veya debug sırasında watchdog resetin istenmediği durumda R128 sökülerek watchdog reset hattı izole edilebilir.

Decoupling ve layout notu

Watchdog entegresinin VCC‑GND beslemesi, gürültülü pano ortamında kararlı olmalıdır. Bu nedenle entegreye çok yakın:

- Cdec = 100 nF (X7R, 0402/0603)

kullanılması önerilir. Ayrıca WDI/WDO izleri yüksek dv/dt hatlardan ve modem RF bölgesinden mümkün olduğunca uzak tutulmalıdır.

Komponent seçimi

Ana entegre

- U23: MAX6369KA‑T (SOT‑23‑8, open‑drain WDO, 100 ms pulse)

Alternatifler (aynı aile)

- MAX6370: push‑pull WDO, kısa pulse (1 ms) isteyen tasarımlar

- MAX6371/MAX6372: startup delay sabit 60 s, watchdog timeout pin seçilebilir

- MAX6373/MAX6374: daha hızlı zaman aralıkları / “first edge” başlatma opsiyonları

Pasifler

- R125, R126, R127: 47k, 1%, 0402 (SET pin pull‑up)

- R129: 47k, 1%, 0402 (WDI pull‑down)

- R128: 0R, 0402 (WDO → MASTER_RESET servis link)

- C152: 33 pF, C0G/NP0, 0402 (WDI EMI yumuşatma)

- Cdec: 100 nF, X7R, 0402 (U23 besleme bypass)

Tahmini maliyet analizi (watchdog bloğu)

Aşağıdaki maliyetler tahmini olup tedarikçiye, miktara ve paketleme opsiyonlarına göre değişir.

| Kalem | Adet | Seçilen | Tahmini Birim | Tahmini Toplam |

|---|---|---|---|---|

| Watchdog IC | 1 | MAX6369KA‑T | 1.25 | 1.25 |

| 47k 1% 0402 | 4 | R125/126/127/129 | 0.005 | 0.020 |

| 0R 0402 | 1 | R128 | 0.005 | 0.005 |

| 33 pF C0G 0402 | 1 | C152 | 0.010 | 0.010 |

| 100 nF X7R 0402 | 1 | Cdec | 0.008 | 0.008 |

| Toplam | 1.29 |

Boot akışı ve güvenli moda geçiş

Reset sonrası ilk hedef, sahada yanlış röle sürüşü / istenmeyen pompa çalışması gibi riskleri sıfırlamaktır. Bu nedenle reset sonrası davranış iki katmanda ele alınır.

Donanım seviyesi: varsayılan güvenli durum

MCU resetten çıktığı anda GPIO’lar bir süre input / tri-state davranışındadır. Bu aralıkta röle sürücü devreleri, MCU’dan bağımsız olarak “OFF” kalacak şekilde tasarlanmalıdır (ör. sürücü girişlerinde uygun pull-down/pull-up, aktif-seviye seçimi). Hedef:

- Röleler enerjisiz (OFF)

- Çıkışlar fail-safe seviyede

Firmware seviyesi: açılışta güvenli konfigürasyon

Firmware açılışının ilk milisaniyelerinde, IO yönleri ve varsayılan seviyeler deterministik biçimde ayarlanmalıdır:

- Kritik çıkışlar OFF seviyesine çekilir (röle sürüşleri, modem güç kontrolü vb.).

- Girişler okunur ve temel durum seti oluşturulur (şebeke var/yok, pompa durumu, termik vb.).

- İletişim katmanı (GSM/RS‑485) kontrollü olarak devreye alınır.

- Sistem “normal çalışma” durumuna geçer.

Watchdog besleme (kick) politikası

Watchdog’un gerçek değer üretmesi için “her yerde kick” yaklaşımından kaçınılmalıdır. Önerilen disiplin:

- WDI toggling yalnızca sistem sağlıklı ana döngüye girdikten sonra başlatılır.

- Eğer kritik bir alt sistem (modem, ölçüm, IO) hata durumuna düşerse; sistemin kendi kendini toparlaması bekleniyorsa bile watchdog besleme “koşullu” yapılır.

Bu sayede yazılım hatalarında sistemin sonsuza kadar aynı hatada kalması yerine, watchdog reset ile toparlanması sağlanır.

Doğrulama ve test önerileri

- BOR testi: 3V3 hattı kontrollü düşürülerek BOR tetiklenme davranışı doğrulanmalı; reset döngüsü ve IO güvenli durumu gözlenmeli.

- Watchdog testi: Firmware’de WDI beslemesi kasıtlı durdurulup watchdog resetin oluştuğu doğrulanmalı.

- EMI testi: WDI hattında parazit kaynaklı yanlış tetik/yanlış besleme ihtimali osiloskopla gözlenmeli; gerekirse RC değerleri optimize edilmeli.

- Fail-safe çıkışlar: Reset anında röle sürücü girişlerinin seviyeleri ölçülmeli; rölelerin yanlış enerjilenmediği doğrulanmalı.