Şematik Tasarım Kontrol Listesi

Bu kontrol listesi, şematik tasarımın okunabilirliğini, üretime uygunluğunu ve test edilebilirliğini güvence altına almak için hazırlanmıştır. Her madde, uygulama sırasında dikkat edilmesi gereken kısa açıklamalar içerir.

Görsel Yapı ve Sayfa Bilgileri

1. Bilgi blokları eksiksiz mi?

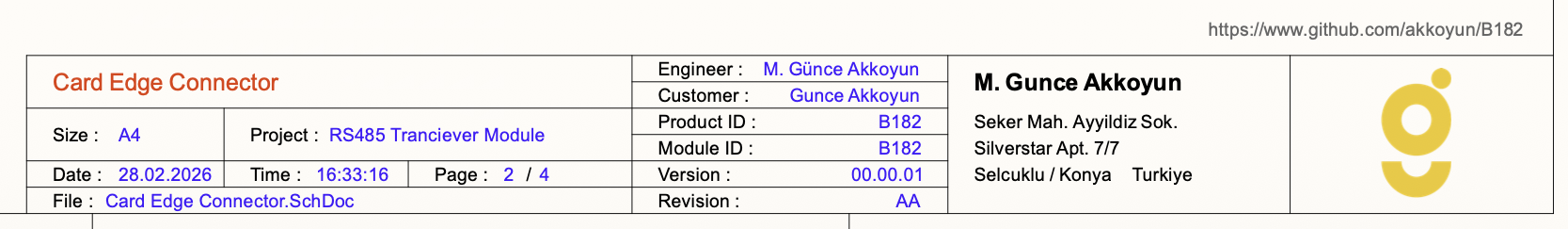

Her şematik sayfada; proje başlığı, müşteri veya ürün adı, modül kodu, versiyon (veya varyant) numarası, tasarım mühendisi adı, GitHub veya kaynak kontrol adresi, sayfa boyutu, tarih-saat damgası, sayfa numarası, dosya adı ve telif notu gibi temel bilgi blokları yer almalıdır.

Bu meta veriler, üretim ve denetim süreçlerinde izlenebilirliği sağlar, revizyon yönetimini kolaylaştırır ve mühendislik disiplinleri arasında ortak bir referans noktası oluşturur.

2. Şematik ölçeği ve okunabilirlik uygun mu?

Sembol boyutları, metin yüksekliği, pin ve net isimleri kolayca okunabilir olmalıdır. Bunun için ölçülebilir bir görsel standart kullanın:

- Referans ve değer metinleri: minimum 4.5 pt, önerilen 5.0–6.0 pt.

- Net label / pin isimleri: minimum 5.0 pt, kritik hatlarda (RESET, clock, güç) 5.5 pt ve üzeri.

- Sayfa başlığı / blok başlıkları: minimum 7.0 pt, alt sistem başlıklarında 8.5 pt tercih edilir.

- Sembol-pin aralığı: metin ile pin arasında en az 2.0–3.0 pt boşluk bırakılmalı.

- Komponentler arası görsel boşluk: yoğun bölgelerde dahi en az 5.5 pt bırakılarak üst üste binme engellenmeli.

Ek kontrol: Şematiği hem editörde %100 yakınlaştırmada hem de A3/A4 PDF çıktısında (fit-to-page olmadan) okuyup pin adı, net adı ve değerlerin ilk bakışta seçilebildiğini doğrulayın. Aşırı sıkıştırılmış, üst üste binen veya farklı ölçeklerde çizilmiş semboller, tasarım hatalarının en yaygın kaynaklarındandır.

3. Sayfa düzeni akışa uygun mu (soldan giriş, sağa çıkış)?

Sinyal ve güç akışı genel olarak soldan sağa, yukarıdan aşağıya olacak şekilde düzenlenmelidir. Bu düzen, şematiğin doğal bir okuma yönü oluşturmasını ve inceleme sırasında mantıksal bağlantıların daha kolay takip edilmesini sağlar. Blok diyagram benzeri bir akış, tasarımın sistematik olarak algılanmasına yardımcı olur.

Uygulamada aşağıdaki düzen kurallarını hedefleyin:

- Giriş/çıkış yerleşimi: harici girişler sayfanın solunda, çıkışlar sağında konumlanmalı; güç girişi üst-sol, yük/dağıtım noktaları orta-sağda tutulmalı.

- Fonksiyon blok sırası:

Power → Koruma → İşlemci/Denetim → Arabirim/Çıkışdizilimi korunmalı; blok sırası sinyal yönüne ters düşmemeli. - Net yönü: ana sinyallerde sola dönen uzun hatlardan kaçınılmalı; gerekli dönüşlerde isimli net label ile kısa atlama tercih edilmeli.

- Çapraz hat sayısı: kritik sayfalarda görünür wire crossing sayısı mümkünse sıfır, yoğun sayfalarda en fazla 3–5 olacak şekilde sınırlandırılmalı.

- Jump/bağlantı noktası kullanımı: T bağlantılarında junction noktası zorunlu olmalı; sadece kesişen ama bağlı olmayan hatlarda junction kullanılmamalı.

- Bus ve kontrol hatları: veri yolları paralel, kontrol hatları ayrı ve etiketli tutulmalı; bus giriş/çıkış uçlarında bit yönü (örn.

[7..0]) iki tarafta da aynı gösterilmeli.

Ek kontrol: Bir ekip üyesi sayfayı ilk kez açtığında, 15–30 saniye içinde sinyalin nereden girip nereye çıktığını ve ana fonksiyon bloklarını okuyabiliyorsa akış düzeni yeterince nettir.

4. Giriş sayfası ve indeks / revizyon notları mevcut mu?

Projenin ilk sayfası; genel sistem mimarisini, alt modülleri ve varsa varyantları tanıtmalıdır. Ayrıca sayfa indeksleri, sembol lejandı, kullanılan kısaltmalar ve revizyon geçmişi burada yer almalıdır. Bu sayfa, özellikle yeni katılan mühendisler veya dış denetçiler için hızlı bir oryantasyon sağlar.

Giriş sayfasında en az aşağıdaki alanlar bulunmalıdır:

- Sistem özeti: kartın amacı, ana kullanım senaryosu, kritik çalışma voltajları ve temel haberleşme arayüzleri (örn. CAN, RS-485, I²C, SPI).

- Blok mimari özeti: her alt modül için kısa açıklama (

Power,MCU,RF,Sensör,Arabirim) ve ilgili sayfa numarası. - Sayfa indeksi:

Sayfa No / Sayfa Adı / Alt Sistem / Sorumlusütunlarıyla listelenmiş içerik tablosu. - Lejand ve kısaltmalar: net isim ekleri (

_N,_P,_EN), sembol işaretleri ve kullanılan tüm kısaltmaların açıklaması. - Varyant bilgisi:

Base / Lite / Progibi varyantlar için hangi sayfaların ortak, hangilerinin varyanta özel olduğu.

Revizyon notlarında aşağıdaki kayıt standardını koruyun:

- Asgari revizyon alanları:

Rev,Tarih,Değişikliği yapan,ECO/Issue No,Özet,Etkilenen sayfalar. - İzlenebilirlik kuralı: her revizyon notu bir commit, issue veya ECO kaydıyla ilişkilendirilmeli.

- Yayın disiplini: üretime çıkan her sürüm için giriş sayfasındaki revizyon tablosu güncellenmeden dosya yayınlanmamalı.

Ek kontrol: Projeye yeni katılan bir mühendis yalnızca giriş sayfasını okuyarak 5 dakika içinde sistem bloklarını, kritik hatları ve hangi sayfadan başlayacağını anlayabiliyorsa bu bölüm yeterli olgunluktadır.

5. Büyük bölüm başlıkları ve sayfa numarası standardı var mı?

Her sayfa, içerdiği alt sistemi açık bir biçimde belirtmelidir (örneğin "Power Regulation", "MCU Interface", "RF Front-End" gibi). Sayfa adlandırma standardı, hem versiyon kontrolü hem de ekip içi iletişim açısından kritiktir. Numaralandırmada tutarlılık, dokümantasyonun sürdürülebilirliğini artırır.

Pratikte tek bir format belirleyip tüm projede aynı şekilde uygulayın:

- Sayfa kodu formatı:

SS-NN(ör.PWR-01,MCU-02,COM-03). - Sayfa başlık formatı:

SS-NN | Alt Sistem | İşlev(ör.PWR-01 | Güç Yönetimi | 3V3 Regülasyon). - Numara mantığı: her alt sistem kendi içinde 01’den başlar; araya sayfa ekleme ihtimali için gerekirse

10adımlı ilerleyin (PWR-10,PWR-20). - Varyant eki: varyanta özel sayfalarda kod sonuna ek kullanın (

-L,-P,-OEM) ve indekste bunu açıkça belirtin. - Dil ve terim tutarlılığı: aynı projede Türkçe/İngilizce başlıklar karıştırılmamalı; tek terim sözlüğü kullanılmalı.

- Rezerve sayfalar: gelecekte eklenecek kritik bloklar için boş kod aralıkları ayrılmalı (örn.

RF-30sonrası rezerve).

Hızlı denetim:

- İndekste geçen her sayfa kodu, şematik başlığında birebir aynı mı?

- Aynı alt sistemde tekrar eden veya atlayan sayfa numarası var mı?

- Off-page referanslarında kullanılan sayfa kodu, hedef sayfanın gerçek koduyla eşleşiyor mu?

6. Sayfalar arası geçiş referansları net mi?

Off-page konektörleri, veri yolları ve net isimleri, bağlandıkları hedef sayfaların numaralarıyla açık şekilde işaretlenmelidir. Bu uygulama, özellikle çok sayfalı projelerde sinyal izleme süresini ciddi biçimde azaltır ve devre mantığının bütünlüğünü korur.

Takibi kolaylaştırmak için tek tip bir referans formatı kullanın:

- Etiket formatı:

NET_ADI | KaynakSayfa → HedefSayfa(örn.UART1_TX | MCU-02 → COM-01). - Yön bilgisi: sinyal yönü tek taraflıysa ok (

→) zorunlu olmalı; çift yönlü hatlarda↔veyaBIDIRifadesi kullanılmalı. - Bus gösterimi: çok bitli hatlarda aralık açık yazılmalı (

DATA[7..0]) ve iki sayfada da aynı bit sırası korunmalı. - Kenar yerleşimi: bir sayfadan çıkan off-page etiketi mümkünse sağ kenarda, gelen etiket sol kenarda konumlandırılarak okuma yönü korunmalı.

- İsim tutarlılığı: aynı sinyal farklı sayfalarda farklı isimle geçmemeli (

MCU_RST_NveRESET_Ngibi çift isimlendirmeden kaçınılmalı). - Güç net istisnası: global güç netleri (

+3V3,GND) için gereksiz off-page connector yerine net adı standardı korunmalı.

Hızlı denetim:

- Her off-page etiketinin karşı sayfada birebir eşi var mı?

- Etikette yazan hedef sayfa kodu gerçekten o sinyalin bulunduğu sayfayı gösteriyor mu?

- Aynı net için birden fazla alternatif ad veya yön çelişkisi bulunuyor mu?

7. Hat türleri renklerle ayrıldı mı?

Şematikte sinyal türleri (örneğin güç, analog, dijital, iletişim, kontrol) farklı renklerle veya çizgi stilleriyle görsel olarak ayrılmalıdır. Bu uygulama, hem okunabilirliği artırır hem de hata incelemesi sırasında hat türlerinin kolayca ayırt edilmesini sağlar. Özellikle büyük projelerde veya ekip çalışmasında, görsel standardizasyon ciddi zaman kazandırır.

Görsel sınıflandırma standardı önerisi:

- Renk sözlüğü: güç/analog/dijital/RF/kontrol için sabit renk eşlemesi dokümante edilmeli.

- Alternatif gösterim: renk körlüğü veya siyah-beyaz çıktı için çizgi stili/kalınlık farkı eklenmeli.

- Tutarlılık: aynı sinyal türü tüm sayfalarda aynı görsel kodu kullanmalı.

- Kritik hat vurgusu: reset, clock, high-current hatlar ek vurgu ile işaretlenmeli.

- Çıktı uyumu: PDF baskıda da ayırt edilebilirlik korunmalı.

Hızlı denetim:

- Renk/stil sözlüğü proje içinde tanımlı ve uygulanmış mı?

- Siyah-beyaz çıktıda hat türleri hâlâ ayırt edilebiliyor mu?

- Ekipte herkes aynı görsel kodları kullanıyor mu?

İsimlendirme, Simgeler ve Referanslar

8. Tüm komponentlere referans kodu verildi mi?

Her bileşen, benzersiz bir referans koduna sahip olmalıdır (örneğin R1, C10, U3). Bu kodlar, hem BOM (Bill of Materials) takibinde hem de montaj sırasında izlenebilirlik sağlar. Eksik veya tekrarlanan referanslar, üretim hatalarının en yaygın nedenlerinden biridir. Revizyon sonrası kontrol listelerinde mutlaka bu uyumu doğrulayın.

Uygulamada aşağıdaki kuralları sabitleyin:

- Benzersizlik kuralı: aynı projede hiçbir referans kodu tekrar etmemeli;

R105yalnızca tek bir bileşene ait olmalı. - Ön ek standardı: bileşen tipine göre sabit prefix kullanılmalı (

R,C,L,D,Q,U,J,TP,F,FB). - Numaralandırma yöntemi: blok bazlı aralık ayırın (örn.

PWR: R100–R199,MCU: R200–R299); böylece hata ayıklama hızlanır. - Çoklu ünite elemanlar: çok parçalı entegrelerde ortak referans korunmalı (

U8A/U8B/U8C) ve tüm üniteler dokümante edilmeli. - DNP parçalar: takılmayacak bileşenler de referans kodu almalı; durumları BOM’da

DNPolarak açıkça işaretlenmeli. - Test ve servis noktaları: test noktaları normal komponentlerden ayrı prefix ile (

TP1,TP2) numaralandırılmalı.

Hızlı denetim:

- ERC/netlist raporunda duplicate designator var mı?

- Şematikteki tüm referans kodları BOM’da birebir karşılık buluyor mu?

- Revizyon sonrası eklenen yeni parçalar, doğru blok aralığında ve sıra bozmadan numaralandırıldı mı?

9. Referans kod formatı standart mı?

Referans kodlarının formatı ekip içinde tanımlanmış bir standarda uygun olmalıdır. Örneğin; Q01, R105 veya çok parçalı entegreler için U8A / U8B biçimi tercih edilmelidir. Tutarlı bir isimlendirme, otomatik test sistemleri, netlist çıkarımı ve BOM entegrasyonu gibi süreçlerde hatasız çalışmayı sağlar.

Standart bir format sözleşmesi belirleyin ve tüm projede aynı kuralları uygulayın:

- Temel format:

PREFIX + NUMARA(örn.R105,C212,U8,J3). - Sıfır dolgu kuralı: aynı prefix grubunda tek basamak/çift basamak karışmamalı (

R1veR01birlikte kullanılmamalı). - Çoklu ünite formatı: çok kapılı entegrelerde

U8A/U8B/U8Cbiçimi zorunlu olmalı. - Test noktası formatı: test noktaları yalnızca

TPprefix’i ile adlandırılmalı (TP1,TP25). - Yasaklı karakterler: referans kodunda boşluk, tire, nokta veya Türkçe karakter kullanılmamalı.

- Yeniden kullanım yasağı: çıkarılan bir bileşenin referans kodu aynı revizyonda başka bileşene tekrar atanmamalı.

Örnek format denetimi (ekip standardı):

- Geçerli:

R105,C22,U8A,FB3,TP12 - Geçersiz:

R-105,R 105,u8a,Tp12,R01+R1(aynı projede)

Hızlı denetim:

- Prefix bazında karışık yazım var mı (örn.

TP01veTP1birlikte)? - Çoklu ünite entegrelerin tüm alt birimleri aynı ana referansı paylaşıyor mu?

- BOM export’unda referans kodları ASCII ve tek formatta görünüyor mu?

10. Birim ve format standartları korundu mu?

Elektriksel değerlerin yazımında uluslararası biçimler kullanılmalıdır: 3.3V → 3V3, 2.2uF → 2u2 gibi. Nokta (.) karakteri, net isimlerinde veya değerlerde kullanılmamalıdır çünkü bazı CAD araçları bunu ondalık ayırıcı olarak yorumlayabilir. Tutarlı bir format, hem şematik hem PCB aşamalarında veri bütünlüğünü garanti eder.

Pratik bir yazım standardı oluşturun ve tüm dosyalarda aynı biçimi koruyun:

- Gerilim yazımı:

3V3,1V8,5V0(net isimlerinde nokta kullanılmamalı). - Direnç yazımı:

4k7,10k,1R0(ondalık nokta yerine harfli gösterim tercih edilmeli). - Kapasitör yazımı:

100nF,2u2,10uF; ASCII gerekiyorsaµyerineutek tip kullanılmalı. - Endüktans yazımı:

4u7H,10uH,1mH. - Akım/frekans yazımı:

250mA,1A,16MHz,400kHz. - Tolerans ve güç: değer yanında ayrı alanda verilmesi tercih edilir (

1%,0.1W); değer alanına karışık metin eklenmemeli.

Doğru / yanlış örnekler:

- Doğru:

3V3,4k7,2u2,100nF,16MHz - Yanlış:

3.3V(net adı olarak),4.7k,.1u,100 nF(format karışık),16Mhz

Hızlı denetim:

- Aynı birim için birden fazla yazım stili var mı (

uFveµFkarışık gibi)? - Net isimlerinde nokta, boşluk veya yerel karakter bulunuyor mu?

- BOM export sonrası değer alanları, üretici tarafında parse edilebilir tek formatta mı?

11. Sembol kütüphaneleri doğru pin eşlemesine sahip mi?

Özellikle özel veya harici eklenen parçalar için, sembol üzerindeki pin numaralarının üretici datasheet'leriyle uyumlu olup olmadığı mutlaka kontrol edilmelidir. Yanlış pin eşleşmeleri, devre kartı üretiminde tespit edilmesi en zor ve en maliyetli hatalardan biridir.

Bu maddeyi geçmek için aşağıdaki eşleşme kontrollerini uygulayın:

- Pin numarası eşleşmesi: semboldeki her pin numarası datasheet pinout tablosuyla birebir aynı olmalı.

- Pin adı/fonksiyon eşleşmesi:

SCL,SDA,BOOT0,EN,VREFgibi fonksiyon isimleri datasheet ile çelişmemeli. - Pin tipi doğruluğu:

Power Input,Input,Output,I/O,Passivesınıfları doğru atanmalı (ERC güvenilirliği için kritik). - Footprint pin map: sembol pin numarası ile footprint pad numarası çapraz kontrol edilmeli;

pin-swap/gate-swapkullanılıyorsa kuralı dokümante edilmeli. - NC ve DNU pinler: datasheet’te

NC,DNU,RESERVEDolan pinler sembolde açıkça işaretlenmeli ve yanlışlıkla routable bırakılmamalı. - EP/thermal pad: exposed pad numarası ve bağlantı tipi (örn.

GND,AGND) hem sembolde hem footprintte aynı olmalı.

Önerilen doğrulama disiplini:

- Yeni kütüphane parçası eklendiğinde 2 kişiyle

symbol-vs-datasheetçapraz kontrol yapılmalı. - İlk prototip öncesi kritik entegreler için (MCU, PMIC, RF, konektör) pin-map checklist’i imzalı tutulmalı.

Hızlı denetim:

- Semboldeki pin sayısı datasheet paketindeki toplam pin sayısıyla eşit mi?

- Güç/ground pinlerinden herhangi biri eksik, gizli veya yanlış isimli mi?

- Netlistte footprint eşleşmesi sonrası "unconnected/short" uyarıları pin-map hatasına işaret ediyor mu?

12. Sembollerde gerekli parametreler var mı?

Kritik bileşenlerde, minimum/maksimum çalışma voltajı, sıcaklık aralığı, akım sınırı veya paket tipi gibi parametreler şematik sembolünde veya açıklama alanında belirtilmelidir. Bu bilgiler, tasarım incelemelerinde ve DRC (Design Rule Check) süreçlerinde mühendislik doğrulamasını hızlandırır.

Sembol seviyesinde zorunlu alan seti tanımlayın ve boş geçilmesine izin vermeyin:

- Elektriksel sınırlar:

Vmin/Vmax,Imax(gerekliysePmax) ve kritik pinler için izinli giriş/çıkış aralığı. - Çevresel sınırlar: çalışma sıcaklığı aralığı (

Tmin/Tmax) ve gerekiyorsa otomotiv/endüstriyel sınıf bilgisi. - Paket bilgisi:

Package,Footprint, pin sayısı veEP(exposed pad) durumu. - Kimlik alanları:

Value,Part Number/MPN,Internal PN(kurum içi kod varsa),Lifecycle(Active/NRND/EOL). - Montaj bilgisi:

DNPdurumu, montaj tipi (SMT/TH) ve polarite gereksinimi. - Doğrulama alanı:

Library Revision,Checked By,Checked Dategibi kütüphane kalite izi.

Önerilen uygulama:

- Kritik parçalar için boş parametreli sembol ERC/CI aşamasında hata kabul edilmeli.

- Parametre isimleri tüm kütüphanede tek sözlükle kullanılmalı (

Vmax/MaxVoltagekarışmamalı).

Hızlı denetim:

- MCU, PMIC, regülatör, MOSFET ve konektörlerde zorunlu alanların tamamı dolu mu?

- Şematikte görülen değerlerle BOM alanları arasında çelişki var mı?

- Revizyon değiştiğinde sembol parametre güncellemesi de aynı değişiklik setine dahil edilmiş mi?

13. Üretici adı şematikte yer almıyor mu (genelde)?

Şematik tasarımlar, üretici bağımsız olmalıdır. Üretici adı, MPN (Manufacturer Part Number) veya tedarikçi bilgileri yalnızca BOM dokümanında tutulmalıdır. Bu ayrım, alternatif komponent seçimini ve tedarik yönetimini kolaylaştırır.

Bu ayrımı korumak için veri katmanlarını net ayırın:

- Şematikte kalacak bilgiler: fonksiyonel değer (

10k,100nF), tolerans/sınıf (gerekiyorsa), referans kodu, net isimleri, elektriksel notlar. - BOM’da tutulacak bilgiler:

Manufacturer,MPN,Supplier,Supplier PN,Lifecycle,Lead Time,Approved Vendor. - Opsiyonel köprü alanı: şematikte yalnızca kurum içi parça kodu (

Internal PN) gösterilebilir; üretici detayı yine BOM tarafında kalmalı. - Alternatif yönetimi: muadil parçalar BOM’da

ALT1/ALT2veya Approved List olarak tutulmalı, şematik bu listeden bağımsız kalmalı. - Revizyon güvenliği: üretici değişikliği (same fit/form/function) yalnızca BOM revizyonu ile yönetilebilmeli; şematik revizyonunu zorunlu kılmamalı.

- İstisna durumu: üreticiye bağımlı özel modül/konnektörlerde not düşülebilir; bu durum açıkça

single-sourceolarak etiketlenmeli.

Hızlı denetim:

- Şematik metinlerinde üretici/tedarikçi adı veya doğrudan MPN geçiyor mu?

- Aynı şematik değer için BOM’da en az bir onaylı alternatif tanımlı mı?

- Sadece tedarik değişikliği yapılan güncellemelerde şematik diff oluşmadan BOM güncellenebiliyor mu?

14. Kütüphane öğelerinde datasheet / link alanları mevcut mu?

Her sembol veya bileşen kütüphanesinde, datasheet bağlantısı için bir alan bulunmalıdır. Bu sayede tasarımcı, bileşen özelliklerine anında erişebilir ve yanlış kullanım riskini minimize eder. Ayrıca ekip içi bilgi paylaşımını hızlandırır ve mühendislik sürecinin sürekliliğini destekler.

Kütüphane kalitesi için minimum link metadata standardı tanımlayın:

- Zorunlu alanlar:

Datasheet URL,Datasheet Rev,Last Checked Date,Source(üretici/resmi dağıtıcı). - Link tipi: mümkünse üreticinin kalıcı ürün sayfası veya resmi PDF bağlantısı kullanılmalı; geçici mirror linklerden kaçınılmalı.

- Doküman eşleşmesi: kullanılan paket/pinout ile aynı varyant datasheet’i bağlanmalı (benzer ama farklı suffix parçalara dikkat).

- Arşiv yaklaşımı: kritik parçalar için kurum içi arşiv kopyası veya checksum referansı tutulmalı.

- Ek dokümanlar: application note, reference design ve errata bağlantıları ayrı alanlarda saklanmalı.

- Erişim disiplini: linke tıklandığında 1–2 adımda ilgili pinout/elektriksel tabloya ulaşılabilmeli.

Önerilen bakım rutini:

- Çeyreklik kütüphane bakımında kırık link taraması yapılmalı.

- Datasheet revizyonu değişen kritik parçalarda (MCU, PMIC, RF, konektör) yeniden inceleme kaydı açılmalı.

Hızlı denetim:

- Kütüphanedeki kritik parçaların tümünde çalışır

Datasheet URLvar mı? - Linklenen doküman ile semboldeki pin/paket bilgisi birebir uyuşuyor mu?

- Son kontrol tarihi 12 ayı aşan kritik bileşen var mı?

Bağlantı Kuralları ve Net Yönetimi

15. Pin yönleri doğru mu? (IN / OUT / I/O / POWER / GND)

Her pinin yönü, bileşenin işlevine uygun olarak tanımlanmalıdır. Giriş, çıkış veya çift yönlü (I/O) pinlerin doğru sınıflandırılması, EDA araçlarının ERC (Electrical Rule Check) işlemleri için kritiktir. Yanlış tanımlanmış pin yönleri, kısa devre veya sürücü çakışmalarına neden olabilir.

Pratik bir pin tipi matrisi uygulayın:

- IN: buton girişleri, ADC girişleri, dijital komut girişleri (

EN,BOOT,INT_IN). - OUT: regülatör çıkışları, buffer/sürücü çıkışları, clock output pinleri.

- I/O: MCU GPIO, bidirectional data hatları (

SDA, bazıD[ ]hatları), konfigüre edilebilir pinler. - POWER INPUT:

VDD,VCC,AVDD,VBATgibi besleme girişleri. - POWER OUTPUT: LDO/DC-DC çıkış pinleri, referans güç üreten pinler.

- PASSIVE/NC: direnç, kapasitör, ferrit, konektör pasif pinleri ve bilinçli

NCuçları.

ERC güvenliği için ek kurallar:

- Output-to-output çakışmaları sıfır toleransla ele alınmalı; zorunlu durumlarda net etiketiyle açıklama notu eklenmeli.

- Power pinler generic

Passivebırakılmamalı; mümkün olduğunca doğru power tipi atanmalı. - Open-drain/open-collector çıkışlar, gerekiyorsa

Open Collectorveya eşdeğer tipte tanımlanmalı. - Kütüphane güncellemesinde pin tipi değiştiyse ilgili sayfada ERC tekrar çalıştırılmalı.

Hızlı denetim:

- ERC raporunda "pin type conflict" veya "driver conflict" uyarısı var mı?

- MCU ve konektör pinlerinde varsayılan

Passivekalmış kritik pin bulunuyor mu? - Güç üreten pinlerden herhangi biri yanlışlıkla

Inputolarak işaretlenmiş mi?

16. Kullanılmayan tüm pinler "NC" ile sonlandırıldı mı?

Bağlantısı yapılmayan (floating) pinler, devrede istenmeyen gürültü, rastgele davranış veya beklenmedik güç tüketimi yaratabilir. Tüm kullanılmayan pinler açıkça NC (No Connect) etiketiyle işaretlenmeli veya datasheet yönergelerine göre uygun şekilde topraklanmalıdır.

Kullanılmayan pin yönetiminde karar sırası şöyle olmalı:

- 1) Datasheet önceliği: pin için üretici “Leave floating / Tie to GND / Tie to VDD / Pull-up/down” ne diyorsa birebir uygulanmalı.

- 2) Dijital giriş pinleri: kural yoksa varsayılan olarak tanımsız bırakılmamalı; uygun değerde pull-up/pull-down ile sabitlenmeli.

- 3) Kullanılmayan çıkış pinleri: genelde açık bırakılabilir; ancak datasheet özel koşul veriyorsa uyulmalı.

- 4) Analog giriş pinleri: gürültüye açık kalmaması için üretici önerisine göre referansa bağlanmalı veya filtreli şekilde sonlandırılmalı.

- 5) Konfigürasyon/strap pinleri: boot mode, adres seçimi gibi pinler mutlaka deterministik seviyeye bağlanmalı.

- 6)

NCetiketi disiplini: gerçekten bağlantısız kalan her pin şematikte görünürNCişareti taşımalı; gizli/yoruma açık bırakılmamalı.

Uygulama notları:

NC,DNUveReservedpinler birbirine karıştırılmamalı;DNU/Reservedpinler için “kesinlikle bağlama” kuralı varsa not düşülmeli.- Çok kapılı entegrelerde kullanılmayan alt kapılar için girişler tanımlı seviyeye çekilmeli, çıkışlar datasheet’e göre sonlandırılmalı.

Hızlı denetim:

- ERC’de floating input uyarısı kalan pin var mı?

- MCU/FPGA üzerindeki kullanılmayan pinler için toplu bir sonlandırma tablosu mevcut mu?

NColarak işaretli pinlerin hiçbiri PCB’de yanlışlıkla route edilmiş görünmüyor mu?

17. Besleme ve GND pinleri açıkça bağlı mı (gizli pin yok)?

Bazı CAD araçları, özellikle entegre devrelerde gizli güç pinleri (hidden power pins) kullanır. Bu pinler görünür olmadığında, güç dağıtımı hataları kolayca fark edilmeyebilir. Şematikte tüm besleme (VCC, VDD vb.) ve toprak (GND) bağlantıları açıkça gösterilmelidir.

Bu maddede hedef, güç ağını herkes için görünür ve izlenebilir tutmaktır:

- Hidden power pin politikası: yeni kütüphane parçalarında gizli güç pini kullanılmamalı; tüm power pinler sembolde görünür olmalı.

- Açık bağlantı kuralı: her

VDD/VCC/AVDD/DVDD/VSS/GNDpini ilgili nete doğrudan bağlanmalı ve net adı okunabilir olmalı. - Analog/dijital ayrımı:

AGND/DGNDveyaAVDD/DVDDayrımları sembolde açıkça etiketlenmeli; birleşim noktası notlandırılmalı. - Çok üniteli entegreler: güç pinleri ayrı “power unit” içinde gizleniyorsa, bu ünite sayfada mutlaka yer almalı ve boş bırakılmamalı.

- Bypass ilişkilendirme: kritik entegrelerin her güç pinine karşılık gelen bypass elemanı şematikte yakın ilişkiyle gösterilmeli.

- Global power sembolleri: global etiket kullanılsa bile güç pininin hangi nete gittiği sayfa üzerinde okunabilir kalmalı.

Yaygın hata önleme notları:

- Farklı voltaj raylarını (

1V8ve3V3gibi) benzer isimle karıştırmayın. GNDyerine yanlışlıklaPGND/AGNDbağlama hatalarına karşı net adını görsel olarak teyit edin.

Hızlı denetim:

- Kütüphane raporunda hidden power pin içeren parça kaldı mı?

- ERC’de unpowered pin veya power net conflict uyarısı var mı?

- Her kritik IC için tüm güç pinlerinin şematikte görünür bağlantısı ve net adı doğrulanabiliyor mu?

18. Güç netleri +/− işaretiyle standart biçimde adlandırıldı mı?

Güç hatları tutarlı bir biçimde isimlendirilmelidir: örneğin +3V3, −1V8, VBAT, +5V_USB gibi. Bu standartlaşma, yanlış voltaj bağlantılarını önler ve güç dağıtım topolojisinin kolay anlaşılmasını sağlar.

Adlandırmayı tek bir şablona bağlayın:

- Temel format:

[İşaret][Seviye][Opsiyonel_Kaynak/Fonksiyon](örn.+3V3,-5V0,+5V_USB,+12V_SYS). - Batarya/ham hatlar:

VBAT,VIN,VRAWgibi fonksiyonel isimler kullanılmalı; belirsiz isimlerden kaçınılmalı. - Regüle hatlar: regülatör çıkışları açıkça ayrıştırılmalı (

+3V3_A,+3V3_D,+1V8_RF). - Toprak adları:

GND,AGND,DGND,PGNDnet ayrımı korunmalı ve birleşim noktası notlanmalı. - Yazım disiplini: aynı ray için tek yazım kullanılmalı (

+3V3ve3V3karışmamalı). - Yasaklı pratikler:

VCC1,PWR_A,SUPPLYgibi voltaj seviyesi belirsiz isimler kritik hatlarda kullanılmamalı.

Doğru / yanlış örnekler:

- Doğru:

+3V3,+5V_USB,VBAT,+1V8_RF,AGND - Yanlış:

3.3V(net adı),VCC,PWR1,5volt,GND1(anlamsız numaralandırma)

Hızlı denetim:

- Aynı voltaj rayı birden fazla isimle geçiyor mu?

- Güç net adı üzerinden voltaj seviyesi ilk bakışta okunabiliyor mu?

- AGND/DGND/PGND ayrımları şematikte tutarlı ve birleşim noktası tanımlı mı?

19. Veri yolu yönleri ve sıraları iki uçta da tutarlı mı?

Çok bitli bus hatlarında (örneğin D[0..7, A[0..15) veya konektörlerde, bit sırası ve yön her iki uçta da birebir aynı olmalıdır. Ters çevrilmiş veya kaymış bit dizilimleri, sistem düzeyinde geri dönüşü zor hata kaynakları oluşturur.

Bus tutarlılığı için aşağıdaki kuralları uygulayın:

- Tek gösterim standardı: bus aralığı projede tek formatta yazılmalı (

[7..0]veya[0..7]), ikisi karışmamalı. - Uçtan uca mapping: kaynak ve hedefte bit eşleşmesi açıkça doğrulanmalı (

D0→D0,D7→D7). - Kasıtlı swap yönetimi: bilerek yapılan bit swap varsa şematik notunda “intentional swap” olarak belirtilmeli.

- Konnektör pin sırası: kablo/harness tarafında terslenme ihtimali için pin numarası + sinyal adı birlikte kontrol edilmeli.

- Bus kırılımı: bus’tan tekil netlere ayrılan yerlerde (

D[7..0]→D0..D7) isimler ve sıra birebir korunmalı. - Saat/valid hatları: veri bus’ına eşlik eden

CLK,CS,VALID,READYgibi kontrol hatları aynı yön mantığıyla etiketlenmeli.

Sık yapılan hatalar:

- Bir sayfada

[7..0], başka sayfada[0..7]kullanmak. - Konnektör giriş/çıkışta ayna etkisiyle bit sırasını ters bağlamak.

- Simetrik isimler nedeniyle (

A1/AI,D0/DO) gözden kaçan yanlış etiketleme.

Hızlı denetim:

- Bus mapping tablosu veya netlist karşılaştırmasında bit kayması var mı?

- Off-page bus etiketlerinde kaynak ve hedef aralık gösterimi aynı mı?

- İlk prototip test planında bus için yürüyen 1/0 (walking bit) doğrulaması tanımlandı mı?

20. Eş sinyaller (UART, I²C, SPI vb.) gruplandı mı?

İlgili sinyallerin bir arada gruplanması, hem okunabilirliği hem de hata ayıklamayı kolaylaştırır. Örneğin UART_TX/RX, SPI_MOSI/MISO/SCK/CS, I2C_SCL/SDA hatları fiziksel olarak yakın konumda ve görsel olarak birlikte gösterilmelidir. Bu yaklaşım, şematikte düzeni korur ve inceleme süresini kısaltır.

Arayüz gruplamasında aşağıdaki standartları uygulayın:

- Protokol bloğu yaklaşımı: her arabirim için tek bir görsel blok oluşturun (

UART1,I2C0,SPI2). - İsim şablonu:

IFACE_INSTANCE_SIGNALformatı kullanın (UART1_TX,I2C0_SCL,SPI2_CS0). - Yerleşim sırası: saat/enable hatları üstte, veri hatları ortada, kontrol/interrupt hatları altta tutulmalı.

- Master/slave yön netliği:

TX/RX,MOSI/MISOgibi isimler taraf bağımlıysa karşı uçta yorum karışmasın diye cihaz adı eklenmeli (MCU_TX,MODEM_RX). - Seviye bilgisi: farklı voltaj domainindeki arabirimlerde net adına veya nota seviye bilgisi eklenmeli (

_1V8,_3V3). - Yakınlık kuralı: ilgili pull-up, termination, ESD ve seri direnç elemanları aynı protokol bloğunun yakınında gösterilmeli.

Sık hata önleme:

- UART hatlarında

TX↔RXçaprazlamasının unutulması. - SPI’de

CShatlarının cihaz bazında ayrıştırılmaması (CSyerineCS_FLASH,CS_ADC). - I²C’de pull-up dirençlerinin bloktan kopuk veya belirsiz nette bırakılması.

Hızlı denetim:

- Her protokol için tüm zorunlu hatlar eksiksiz mi? (UART: TX/RX, I²C: SCL/SDA, SPI: SCK/MOSI/MISO/CS)

- Aynı protokole ait sinyaller sayfada tek bölgede toplanmış ve etiketleri tutarlı mı?

- Arabirim bloğuna bakan bir mühendis 10–15 saniyede bağlantı yönünü ve cihaz eşleşmesini anlayabiliyor mu?

21. Sayfa dışı veri yolları kenar etiketiyle açıkça gösterildi mi?

Farklı sayfalara taşan sinyaller, sayfa kenarında etiketlenmiş off-page connector veya net label ile işaretlenmelidir. Bu, çok sayfalı projelerde sinyal akışını hızlı takip etmeyi sağlar ve bağlantı tutarlılığını garanti eder.

Off-page etiketleme için tek bir sözleşme kullanın:

- Etiket formatı:

NET/BUS_ADI | KaynakSayfa → HedefSayfa(örn.SPI2_MISO | MCU-02 → COM-01). - Bus etiket formatı:

BUS[MSB..LSB] | Kaynak → Hedef(örn.ADC_D[11..0] | ANA-01 → MCU-03). - Yön zorunluluğu: tek yönlü hatlarda ok (

→) zorunlu; çift yönlü hatlarda↔veyaBIDIRyazılmalı. - Kenar yerleşimi: sayfadan çıkan etiket sağ kenarda, giren etiket sol kenarda konumlandırılarak okuma yönü korunmalı.

- Eş etiket kuralı: bir etiketin karşı sayfada birebir eşi bulunmalı; isim/sayfa kodu/bit aralığı tam aynı olmalı.

- Yoğun sayfa yönetimi: aynı kenarda birden fazla off-page varsa grup başlığı veya numaralı sıralama (

OP1,OP2) ile düzenlenmeli.

Sık hata önleme:

- Hedef sayfa kodunun güncellenip etiketin güncellenmemesi.

- Bus aralıklarının karşı sayfada ters veya eksik yazılması.

- Aynı sinyalin farklı sayfalarda farklı adlarla etiketlenmesi.

Hızlı denetim:

- Tüm off-page etiketlerinin karşı sayfada birebir karşılığı var mı?

- Etiketteki kaynak/hedef sayfa kodları mevcut sayfa başlıklarıyla eşleşiyor mu?

- Bus off-page etiketlerinde bit aralığı ve yön bilgisi iki tarafta da aynı mı?

22. Open-collector / open-drain hatlarda uygun pull-up / pull-down dirençleri mevcut mu?

Bu tür hatlar, harici dirençlerle mantıksal seviye belirlenmediğinde kararsız hale gelir. Pull-up veya pull-down dirençlerin doğru konumda ve uygun değerlerde seçildiğinden emin olun. Özellikle I²C, interrupt veya reset hatlarında bu kritik önem taşır.

Direnç seçimini aşağıdaki pratik aralıklarla başlatın, sonra sistem koşullarına göre doğrulayın:

- I²C tipik başlangıç değerleri:

100 kHziçin4k7–10k,400 kHziçin2k2–4k7,1 MHziçin1k–2k2. - Genel open-drain hatlar: çoğu dijital kontrol hattında

4k7–47karalığı uygundur; hız arttıkça direnç düşürülür. - Reset/interrupt hatları: gürültü bağışıklığı ve tüketim dengesi için çoğunlukla

4k7–10ktercih edilir. - Akım sınırı kontrolü: düşük seviyede sürücü akımı, seçilen pull-up ile oluşan sink akımını güvenle taşıyabilmeli.

- Yükselme süresi kontrolü: toplam hat kapasitansı (iz + pin + konektör) ile RC zaman sabiti hedef protokol hızını karşılamalı.

- Voltaj domain uyumu: pull-up hattının bağlı olduğu ray, pinlerin mutlak maksimum ve lojik seviye sınırlarıyla uyumlu olmalı.

Yerleşim ve topoloji notları:

- Pull-up/pull-down elemanı mümkünse ilgili alıcı/sürücü bloğuna yakın yerleştirilmeli.

- Aynı nette birden fazla paralel pull-up olup olmadığı kontrol edilmeli (etkin direnç beklenenden düşmesin).

- Uzun kablo veya dış konektörlü hatlarda EMI için seri direnç/filtre ihtiyacı ayrıca değerlendirilmelidir.

Hızlı denetim:

- Datasheet’te verilen minimum/maksimum pull-up akım ve rise-time şartları sağlanıyor mu?

- Aynı open-drain nette farkında olmadan ikinci bir pull-up bağlı mı?

- Osiloskopta düşük seviye VOL ve yükselme süresi protokol sınırları içinde mi?

23. Aktif-LOW sinyaller çizgiyle (¯) işaretlendi mi?

Aktif düşük (Active-LOW) sinyaller, isimlerinin üstünde bir çizgi (örn. RESET̅, CS̅) veya sonlarında "_N" ekiyle (RESET_N) belirtilmelidir. Bu gösterim standardı, mantık yönünün yanlış anlaşılmasını önler ve tasarım belgeleri arasında tutarlılık sağlar.

Proje genelinde tek bir aktif-LOW konvansiyonu seçin ve karışık kullanım yapmayın:

- Önerilen metin standardı: ASCII uyumu için

_Nveya_Beklerinden biri seçilip tüm projede sabit kullanılmalı (tercihen_N). - Şematik gösterim: eğer üst çizgi (overbar) kullanılıyorsa, net adında yine de metin karşılığı korunmalı (

RESET_N). - Tutarlı isim eşleşmesi: aynı sinyal farklı sayfalarda

RESET_N,nRESET,RESET#gibi farklı biçimlerde geçmemeli. - Aktif-seviye notu: kritik kontrol sinyallerinde (reset, chip-select, enable, fault) gerektiğinde kısa notla aktif seviye belirtilmeli.

- Bidir/çoklu sürücü hatları: active-low open-drain hatlarda isim + sürüş tipi birlikte net olmalı (

INT_N_OD). - Firmware uyumu: donanım isimleri ile firmware pin adları birebir eşlenmeli; ters mantık yazılımda ayrıca belgelenmeli.

Doğru / yanlış örnekler:

- Doğru:

RESET_N,CS_N,PWR_EN_N,FAULT_N - Yanlış:

RESET,nReset,RESET#,CS̅+CS_N(aynı projede karışık)

Hızlı denetim:

- Şematikteki tüm active-low hatlar tek adlandırma kuralını izliyor mu?

- Off-page ve konektör pin isimlerinde aktif-seviye bilgisi kaybolmadan taşınıyor mu?

- Firmware pin map dokümanında active-low hatlar açıkça işaretlenmiş mi?

24. Reset hatları güvenilir bir tasarıma sahip mi?

Reset hattı, sistemin deterministik şekilde başlatılmasını sağlamalıdır. Güç açılışında rastgele durumların oluşmaması için RC tabanlı gecikme devreleri, supervisor IC'ler veya manuel reset butonu gibi önlemler uygulanmalıdır. Bu tasarım disiplini, özellikle mikrodenetleyici tabanlı sistemlerde kararlılığı belirleyen en kritik faktörlerden biridir.

Reset tasarımında aşağıdaki kriterleri hedefleyin:

- Tanımlı varsayılan seviye: reset hattı pull-up/pull-down ile her koşulda kararlı seviyede tutulmalı (

RESET_Niçin genelde pull-up). - Gecikme penceresi: POR (power-on reset) gecikmesi besleme oturma süresini kapsamalı; tipik uygulamalarda

5–50 msaralığı doğrulanmalı. - Supervisor tercihi: besleme toleransı dar veya kritik sistemlerde yalnız RC yerine supervisor/voltage monitor IC kullanılmalı.

- Brown-out davranışı: besleme düşüşünde resetin tetiklenme eşiği (

V_BOR) MCU/SoC gereksinimleriyle uyumlu olmalı. - Harici reset yolu: test ve servis için buton veya debug üzerinden kontrollü reset imkânı bulunmalı.

- Çoklu rail senaryosu: birden fazla besleme hattında reset bırakma zamanı, en geç stabil olan rail’e göre belirlenmeli.

Uygulama notları:

- Reset hattı gürültüye açıksa küçük RC filtre veya seri direnç ile bastırma değerlendirilmeli.

- Watchdog reset, dış reset ve POR kaynakları firmware/debug dokümanında ayrıştırılmalı.

Hızlı denetim:

- Güç açılışında osiloskopta resetin bırakılma zamanı, besleme stabil olduktan sonra mı gerçekleşiyor?

- Brown-out testinde sistem deterministik olarak resetlenip güvenli şekilde tekrar başlıyor mu?

- Reset hattında yanlış tetiklemeye neden olan EMI/parazit gözleniyor mu?

Güç Mimarisi ve Bypass/Decoupling

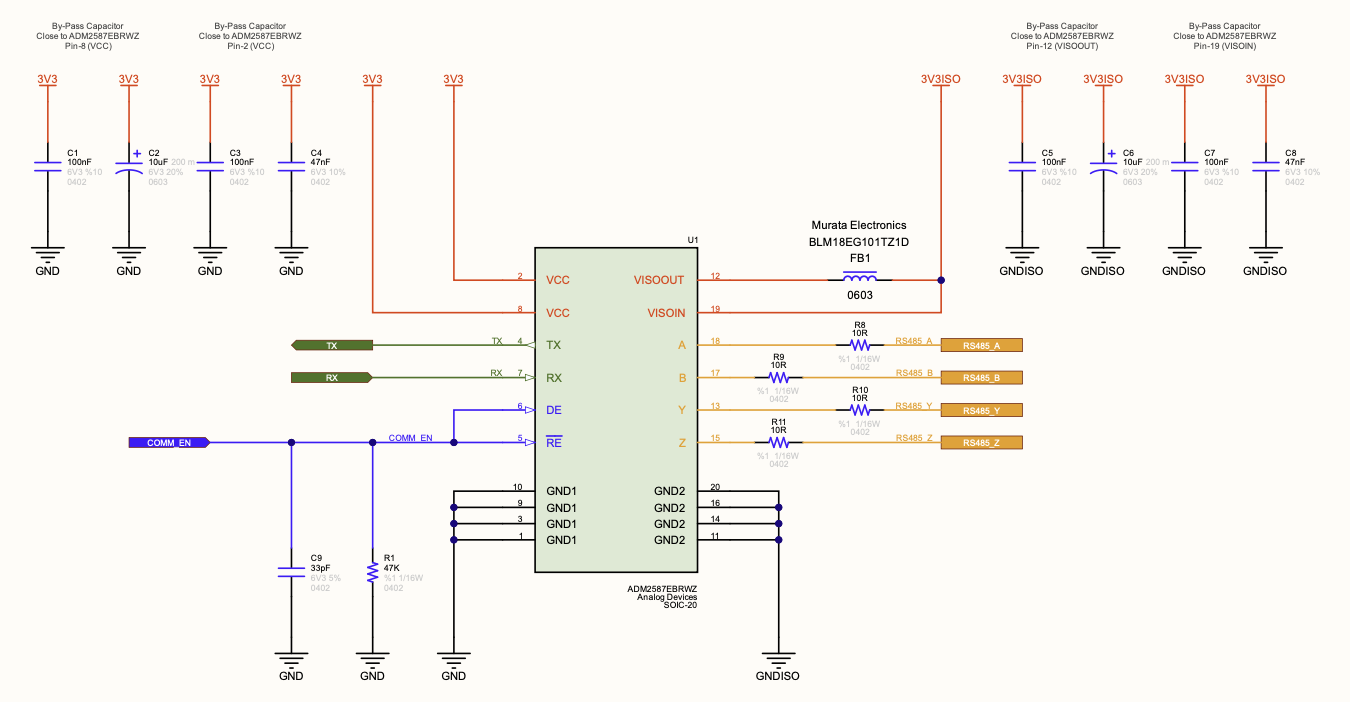

25. Tüm entegrelerin her besleme pininde bypass kapasitörü var mı?

Her entegre devre, kendi besleme pinine mümkün olduğunca yakın konumlandırılmış bypass (decoupling) kapasitörlerine sahip olmalıdır. Genellikle her pin için 100 nF seramik kondansatör eklenir; buna ek olarak, hattın genel kararlılığını sağlamak için uygun değerde bir bulk (örneğin 1–10 µF) kapasite paralel bağlanır. Bu elemanlar, yüksek frekanslı gürültüleri bastırır ve ani akım taleplerinde besleme hattının kararlılığını korur.

Bypass stratejisini aşağıdaki temel kurallarla sabitleyin:

- Pin başına bypass: her güç pinine en az bir adet

100nF(X7R/X5R) decoupling kondansatör atanmalı. - Frekans katmanı: hızlı dijital entegrelerde

100nF + 1uFkombinasyonu tercih edilmeli. - Bulk destek: her güç domaininde ek olarak

4u7–22uFaralığında bulk kapasite bulunmalı. - Ayrı domain:

AVDD/DVDDgibi ayrı hatların bypass elemanları ayrı gösterilmeli. - Seri empedans farkı: ferrit/direnç sonrası oluşan yeni güç adası için ayrı bypass zorunlu olmalı.

Hızlı denetim:

- Her kritik IC’nin tüm power pinleri için şematikte karşılık gelen bypass referansı var mı?

- Sadece “bir tane genel kapasitör” ile geçiştirilmiş güç pin grubu kaldı mı?

- Netlistte power pin sayısı ile bypass ataması arasında açık bir eşleşme kurulabiliyor mu?

26. Bypass kapasitör yerleşim niyeti şematikte notlandı mı?

Her bypass kondansatörünün, beslediği pinin fiziksel olarak en yakınına yerleştirilmesi gerektiği şematik üzerinde açıkça not edilmelidir. PCB tasarımcıları için bu bir hatırlatma değil, bir tasarım kuralıdır. Uzak yerleştirilen bypass elemanları, etkisini büyük ölçüde kaybeder ve EMC sorunlarına yol açabilir.

Şematik notlarında yerleşim niyetini açık ve ölçülebilir ifade edin:

- Yakınlık notu: “Cdec, ilgili VDD pinine en yakın yerleşecek” notu kritik entegrelerde zorunlu olmalı.

- Loop alanı hedefi:

VDD pin → Cdec → GND dönüşüakım döngüsü minimum alanla kurulmalı. - Via disiplini: mümkünse kondansatörün GND ucu doğrudan referans düzleme kısa via ile inmeli.

- Öncelik sırası: birden fazla bypass varsa en küçük değerli kondansatör pine en yakın olmalı.

- Yerleşim referansı: yüksek hızlı bloklarda “same side placement” (aynı yüzey) tercihi notlanmalı.

Hızlı denetim:

- Şematik notlarında bypass yerleşim niyeti açık cümleyle belirtilmiş mi?

- Kritik bloklarda (MCU, FPGA, RF) bypass yerleşim kuralı ayrı notlanmış mı?

- PCB incelemesinde bu notlar uygulanıp uygulanmadığı takip edilebiliyor mu?

27. Analog bloklar için ayrık güç yolu sağlandı mı?

Analog ve dijital devrelerin aynı güç hattını paylaşması, sinyal gürültüsünü önemli ölçüde artırır. Bu nedenle, analog ve dijital besleme yolları ayrılmalı, uygun noktada ferrit bead veya RC filtresi ile birbirine bağlanmalıdır. Bu ayrım, özellikle ADC, DAC, op-amp veya RF devrelerinde ölçüm doğruluğunu belirleyen temel kriterdir.

Analog güç ayrımında uygulanabilir yaklaşım:

- Ayrı net adları:

AVDD/AGNDveDVDD/DGNDnetleri şematikte açıkça ayrılmalı. - Tek birleşim noktası: analog ve dijital topraklar kontrol edilen tek noktada (star-point) birleştirilmeli.

- Besleme izolasyonu: analog besleme, dijital rail’den ferrit bead veya RC filtre üzerinden türetilmeli.

- Yerel bypass: analog IC çevresinde düşük gürültülü bypass kombinasyonu (

100nF + 1uF) ayrı tutulmalı. - Gürültülü yük izolasyonu: anahtarlamalı yükler (DC-DC, motor sürücü, clock) analog raydan fiziksel ve elektriksel olarak ayrılmalı.

Hızlı denetim:

- Şematikte analog ve dijital güç netleri isim bazında ayrılmış mı?

- AGND-DGND birleşim yeri açık ve tekil olarak tanımlanmış mı?

- ADC/DAC referans hattı gürültülü dijital güç dönüşüyle doğrudan paylaşılmıyor mu?

28. LDO giriş/çıkış kapasitans koşulları karşılanıyor mu?

Düşük düşümlü regülatörler (LDO) belirli kapasitans ve ESR (Equivalent Series Resistance) değerlerine ihtiyaç duyar. Her LDO için üretici datasheet'inde belirtilen minimum giriş ve çıkış kondansatör değerleri sağlanmalı; ESR limitleri göz önünde bulundurulmalıdır. Uygun olmayan kapasitör seçimi, osilasyon veya kararsız çıkış gerilimine neden olabilir.

LDO doğrulamasını şu kontrol adımlarıyla yapın:

- Cin/Cout alt sınırı: datasheet’te verilen minimum giriş/çıkış kapasite değeri birebir sağlanmalı.

- ESR penceresi: seçilen kondansatörün ESR değeri LDO stabilite aralığı içinde olmalı.

- Derating etkisi: DC bias ve sıcaklık altında efektif kapasitans düşüşü hesaba katılmalı.

- Ripple/PSRR hedefi: çıkış dalgalanma hedefi için gerekirse ek çıkış kapasitesi veya RC sonrası filtreleme düşünülmeli.

- Yük adımı davranışı: ani yük değişiminde droop/overshoot kabul sınırı karşılanmalı.

Hızlı denetim:

- Her LDO için kullanılan Cin/Cout ve ESR değeri datasheet tablo/örnek devreyle eşleşiyor mu?

- Uygulanan kondansatör dielektriği (X5R/X7R vb.) efektif kapasiteyi kritik seviyenin altına düşürüyor mu?

- Regülatör çıkışında prototip ölçümünde osilasyon veya aşırı ring gözleniyor mu?

29. Güç sıralaması ve enerjilenme senaryoları tanımlı mı?

Birden fazla voltaj hattı bulunan sistemlerde, güç açılış sırası (power-up sequence) net şekilde tanımlanmalıdır. Bazı entegreler, belirli bir voltaj hattı aktif olmadan diğerinin yükseltilmesini tolere etmez. Ayrıca, brown-out veya ani voltaj düşüşleri durumunda sistemin nasıl davranacağı da tasarım notlarında belirtilmelidir. Bu bilgiler, hem firmware hem de donanım güvenilirliği açısından hayati öneme sahiptir.

Power sequencing için net kurallar belirleyin:

- Sıra tanımı: voltaj rayları için açık sıra verin (örn.

+3V3 → +1V8 → +1V2). - Zaman penceresi: rail’ler arası minimum bekleme süresi ve reset bırakma gecikmesi tanımlı olmalı.

- Enable bağımlılığı: PMIC/LDO enable pinleri doğru rail’e bağımlı olacak şekilde bağlanmalı.

- Power-down senaryosu: kapanış sırasındaki ters akım/latch-up riskleri için deşarj ve izolasyon stratejisi bulunmalı.

- Hata durumları: brown-out, UVLO, kısa kesinti senaryolarında sistem davranışı notlanmalı.

Hızlı denetim:

- Sıralama kuralı şematik notu veya ayrı diyagramla dokümante edilmiş mi?

- Kritik IC’lerin “rail before rail” gereksinimleri tek tek doğrulanmış mı?

- Güç açma/kapama testlerinde firmware’in güvenli başlangıç moduna geçtiği doğrulanmış mı?

30. Toplam akım bütçesi (worst-case) hesaplandı mı?

Tüm sistem bileşenlerinin maksimum akım tüketimleri, en kötü senaryoya göre toplanmalı ve güç kaynağının kapasitesi buna göre seçilmelidir. Bu analiz, sadece ortalama akımı değil, anlık (peak) talepleri de içermelidir. Bu hesap, hem regülatör seçimi hem de termal yönetim açısından zorunludur.

Akım bütçesini tablo halinde ve rail bazında çıkarın:

- Rail bazlı toplam: her güç rayı için

I_typ,I_max,I_peakdeğerleri ayrı hesaplanmalı. - Başlangıç akımı: açılış anındaki inrush ve kapasitif yük akımı dahil edilmeli.

- Eşzamanlı yük: tüm yüklerin aynı anda aktif olabileceği en kötü kullanım senaryosu tanımlanmalı.

- Güvenlik payı: güç kaynağı ve regülatörler en az

%20–30tasarım marjıyla seçilmeli. - Termal ilişki: akım artışının regülatör, iz genişliği ve konnektör ısınmasına etkisi birlikte değerlendirilmelidir.

Hızlı denetim:

- Her rail için worst-case akım tablosu dokümana eklenmiş mi?

- Seçilen regülatör ve konnektör akım limiti, hesaplanan

I_peakdeğerinin üzerinde mi? - Ölçüm/test sırasında beklenen ve gerçek akım değerleri kabul edilebilir sapmada mı?

31. Dirençlerin güç değerleri doğrulandı mı?

Kullanılan dirençlerin güç dayanımları (P = V²/R) hesaplanmalı ve uygun paket boyutu seçilmelidir. Uzun süreli kararlılık ve güvenilirlik için, dirençler nominal güçlerinin %50–70'i aralığında çalışmalıdır. Aşırı yüklenen dirençler, zamanla değer kaybı ve termal hasar oluşturur.

Direnç güç doğrulamasını standartlaştırın:

- Temel hesap: her kritik direnç için

P = I²RveP = V²/Rile çapraz kontrol yapılmalı. - Derating kuralı: sürekli çalışmada hedef güç, nominalin en fazla

%50–60seviyesinde tutulmalı. - Darbe yükü: pulsed/surge uygulamalarda pulse handling grafikleri kontrol edilmeli.

- Paket seçimi: 0402/0603 gibi küçük paketlerde sıcaklık artışı ve gerilim limiti ayrıca doğrulanmalı.

- Yüksek gerilim dirençleri: seri direnç zinciri ve creepage/clearance etkileri birlikte değerlendirilmelidir.

Hızlı denetim:

- Güç harcaması yüksek dirençler için hesap tablosu mevcut mu?

- Seçilen direnç watt değeri sıcaklık derating sonrası hâlâ yeterli mi?

- Termal kamera/ölçümde kritik dirençlerde beklenmeyen ısınma var mı?

32. Gerilim bölücü / pull-up / pull-down akımları hesaplandı mı?

Gerilim bölücü devrelerde veya seviye belirleyici dirençlerde akım akışı doğru hesaplanmalıdır. Çok düşük akımlar, girişleri gürültüye açık hale getirirken; gereğinden yüksek akımlar, güç tüketimini artırır. Özellikle pil ile çalışan sistemlerde bu dirençler enerji verimliliğini doğrudan etkiler.

Bu tür direnç ağları için aşağıdaki pratik kuralları uygulayın:

- Gerilim bölücü akımı: ölçüm girişlerinde tipik olarak

10uA–200uAaralığı hedeflenmeli (uygulamaya göre optimize edilir). - ADC kaynak empedansı: ADC girişinin izin verdiği maksimum kaynak empedansı aşılmamalı; gerekirse buffer/op-amp kullanılmalı.

- Pull-up/pull-down seçimi: gürültü bağışıklığı ve tüketim dengesi için çoğu dijital girişte

4k7–100karalığı doğrulanmalı. - Sızıntı akımı etkisi: yüksek değerli dirençlerde pin leakage ve PCB yüzey kaçakları hesapta dikkate alınmalı.

- Tolerans bütçesi: direnç toleransı ve referans gerilim hataları toplam ölçüm doğruluğuna dahil edilmeli.

Hızlı denetim:

- Bölücü çıkış empedansı, bağlı giriş pininin datasheet limitlerine uygun mu?

- Pil modunda gereksiz bölücü akımı sistem bekleme tüketimini bozuyor mu?

- Pull direnci seçimleri EMC/gürültü testlerinde kararlılığı koruyor mu?

33. Çiplerin çektiği akım notlandı mı?

Her büyük entegre (örneğin MCU, FPGA, RF transceiver) için ortalama ve maksimum akım tüketimi şematikte veya not kısmında belirtilmelidir. Bu bilgi, güç kaynağı kapasitesinin doğrulanması, termal analiz ve test planlaması açısından büyük önem taşır. Ayrıca sistemin toplam akım bütçesi oluşturulurken doğrudan referans sağlar.

Akım notlandırma standardı:

- Alan seti:

I_typ,I_peak, çalışma modu ve besleme rayı birlikte belirtilmeli. - Mod bazlı değer: sleep/idle/active/TX gibi modlara göre tüketim ayrıştırılmalı.

- Kaynak referansı: değerlerin datasheet sayfası veya test ölçümü referansı eklenmeli.

- Toplam bütçe bağı: çip akımı ilgili ray toplamına bağlanmalı.

- Revizyon güncelleme: firmware veya clock değişimlerinde akım notu revize edilmeli.

Hızlı denetim:

- Tüm kritik entegrelerde akım notu mevcut mu?

- Mode değişimlerinde akım farkı belgelenmiş mi?

- Ölçülen akım değerleri notlarla uyumlu mu?

34. Güç hattı filtresi ve ferrit boncuk değerleri datasheet'e göre doğrulandı mı?

Ferrit boncuk ve RC filtre bileşenleri, kullanılan entegrelerin üretici önerilerine göre seçilmelidir. Yanlış empedans veya frekans karakteristiğine sahip ferrit, gürültü bastırmak yerine rezonansa neden olabilir. Bu nedenle datasheet'te belirtilen frekans aralığına ve akım kapasitesine uygun ferrit seçimi yapılmalıdır.

Ferrit/filtre doğrulama adımları:

- Empedans frekansı: ferrit seçimi hedef gürültü frekans bandına göre yapılmalı.

- DC akım kapasitesi: boncuk satürasyonu ve sıcaklık artışı sınırları kontrol edilmeli.

- DCR etkisi: güç hattı düşümü ve verim üzerindeki etkisi hesaplanmalı.

- RC cutoff: RC filtrelerde kesim frekansı hedeflenen bastırma bandına uygun seçilmeli.

- Yerleşim: filtre elemanları gürültü kaynağı ve korunacak blok arasında doğru konumlandırılmalı.

Hızlı denetim:

- Seçilen ferrit değerleri datasheet önerileriyle uyumlu mu?

- Filtre sonrası gürültü ölçümlerinde iyileşme görüldü mü?

- Ferrit ısınması/satürasyonu saha koşullarında güvenli mi?

Koruma, Güvenlik ve Uygunluk

35. Kart dışı arabirimler ESD'ye karşı korundu mu?

Dış ortamla temas eden tüm hatlar (örneğin USB, HDMI, UART, butonlar, sensör konektörleri) ESD (Electrostatic Discharge) korumasına sahip olmalıdır. Özellikle kullanıcı tarafından dokunulabilecek konektörler ve metal yüzeyler, transient voltaj darbelerine karşı TVS diyot veya koruma dirençleri ile korunmalıdır. Bu önlem, hem donanım arızalarını hem de saha kaynaklı garanti maliyetlerini önemli ölçüde azaltır.

ESD korumasında minimum tasarım disiplini:

- Koruma elemanı seçimi: hat tipine uygun düşük kapasitanslı TVS/ESD diyot kullanılmalı (özellikle yüksek hızlı hatlarda).

- Konum kuralı: ESD elemanı konektöre mümkün olan en yakın noktada konumlandırılmalı.

- Deşarj yolu: darbe akımı doğrudan GND referansına kısa ve düşük endüktanslı yoldan aktarılmalı.

- Arayüz bazlı yaklaşım: USB, CAN, RS-485, GPIO dış hatları için ayrı koruma topolojisi tanımlanmalı.

- Ortak-mod koruma: diferansiyel hatlarda eşleşmiş koruma elemanları ve gerekirse common-mode choke değerlendirilmeli.

Hızlı denetim:

- Tüm dış konektör pinleri için ESD elemanı eşlemesi yapıldı mı?

- ESD elemanının parasitik kapasitesi ilgili sinyal bütünlüğü bütçesine uygun mu?

- ESD testlerinde (temas/hava) resetlenme veya kalıcı hasar gözleniyor mu?

36. Yüksek voltaj / akım hatları için kurallar belirlendi mi?

Güç hatları için iz genişliği, sigorta, yaklaşma (clearance) ve kaçak (creepage) mesafeleri tasarım standartlarına göre kontrol edilmelidir. IPC-2221 veya UL-60950 gibi standartlar referans alınabilir. Bu kriterler, yalnızca güvenlik değil, uzun vadeli termal dayanım açısından da zorunludur. Ayrıca yüksek akım hatlarında termal via'lar ve bakır kalınlığı yeterli olmalıdır.

Tasarımda şu başlıklar mutlaka hesaplanmalı:

- İz genişliği ve bakır kalınlığı: sürekli/pik akıma göre sıcaklık artışı hedefiyle birlikte belirlenmeli.

- Koruma zinciri: sigorta, akım sınırlama ve ters polarite koruması birlikte değerlendirilmelidir.

- Clearance/creepage: çalışma gerilimine ve kirlenme sınıfına uygun minimum mesafeler tablolanmalı.

- Termal yönetim: yüksek akım düğümlerinde geniş bakır alan, via array ve ısıl yayılım stratejisi planlanmalı.

- Konnektör limiti: konektör pin başına akım limiti ve sıcaklık derating’i kontrol edilmelidir.

Hızlı denetim:

- En yüksek akım hattı için iz genişliği hesabı dokümante edildi mi?

- HV hatlarında clearance/creepage ihlali kalmadı mı?

- Koruma elemanlarının açma/tepki karakteristiği sistem gereksinimine uygun mu?

37. Otomotiv sınıfı modüller için transient dayanımı sağlandı mı?

Otomotiv uygulamalarında besleme hatları 60–100V arası ani gerilim darbelerine (load dump) maruz kalabilir. Bu nedenle, transient voltage suppressor (TVS) diyotlar, LC filtreler ve uygun sigorta elemanları ile koruma yapılmalıdır. ISO 7637 veya ISO 16750 standartları referans alınarak test koşulları tanımlanmalıdır. Bu önlem, aracın elektrik sistemiyle etkileşimde cihazın güvenilir çalışmasını garanti eder.

Otomotiv transient korumasında önerilen yapı:

- Load-dump koruması: uygun standoff/clamp değerine sahip TVS seçilmeli ve enerji kapasitesi doğrulanmalı.

- Ters akü koruması: ideal diyot/MOSFET veya seri koruma elemanıyla negatif besleme senaryosu ele alınmalı.

- ISO pulse kapsamı: en az ISO 7637 pulse senaryoları için test planı oluşturulmalı.

- Filtre zinciri: girişte sigorta + TVS + LC/π filtre kombinasyonu sistem seviyesinde optimize edilmeli.

- Çalışma sıcaklığı: koruma elemanları otomotiv sıcaklık aralığında derating ile değerlendirilmelidir.

Hızlı denetim:

- TVS’nin güç/enerji kapasitesi en kötü transient senaryosunu karşılıyor mu?

- Test planında ISO 7637/16750 pulse maddeleri ve kabul kriterleri net mi?

- Transient sonrası modül, reset veya kalıcı bozulma olmadan normal çalışmaya dönebiliyor mu?

38. CE / FCC / RoHS uygunluğu kontrol edildi mi?

Ürünün tasarım aşamasında CE (Avrupa), FCC (ABD) ve RoHS (zararlı madde kısıtlaması) gereksinimleri göz önüne alınmalıdır. EMC (elektromanyetik uyumluluk) ve güvenlik gereklilikleri üretim sonrasında test edilse de, erken aşamada yapılan tasarım kontrolleri, maliyetli revizyonların önüne geçer. Uygun komponent seçimi, topraklama stratejisi ve filtreleme topolojisi bu süreçte belirleyici rol oynar.

Uygunluk hazırlığını tasarım aşamasında şu şekilde yönetin:

- Ön uygunluk kontrol listesi: CE/FCC için kritik tasarım maddeleri (EMI filtreleri, topraklama, ekranlama) erken doğrulanmalı.

- RoHS veri izi: bileşen bazında RoHS/REACH beyan dokümanları BOM ile eşleştirilmeli.

- Riskli hatlar: yüksek dv/dt ve hızlı kenarlı hatlar için EMI azaltıcı önlemler şematikte görünür olmalı.

- Teste hazırlık: pre-compliance ölçüm noktaları ve test konfigürasyonu dokümante edilmeli.

- Revizyon yönetimi: uygunluğu etkileyen bileşen değişiklikleri ayrı gözden geçirme adımına tabi tutulmalı.

Hızlı denetim:

- BOM’daki tüm kritik parçalar için RoHS kanıtı erişilebilir mi?

- EMI/EMC açısından kritik bloklarda bastırma elemanları tanımlı mı?

- Ürün için pre-compliance test planı (iletilen/yayılan emisyon) hazır mı?

39. Konektör / soket mekanik uyumlulukları doğrulandı mı?

Tüm konektör ve soketlerin mekanik oturma ölçüleri, yönlendirme anahtarları, PCB kalınlığı uyumu ve eşleşen karşı parçaları datasheet'e göre doğrulanmalıdır. Yanlış yön veya tolerans farkı, saha montajında yüksek arıza oranlarına neden olur. Özellikle üretim hattında karışıklığı önlemek için konektör tipi ve yönü şematikte açıkça belirtilmelidir.

Mekanik uyumluluk için zorunlu kontroller:

- Mating doğrulama: konektörün karşı parça kodu ve üretici mating listesi teyit edilmeli.

- PCB stack etkisi: PCB kalınlığı, plaka kaplama ve keep-out bölgeleriyle birlikte kontrol edilmeli.

- Yön/anahtarlama: polarizasyon ve keying yapısı ters takmayı fiziksel olarak engelleyecek şekilde seçilmeli.

- Montaj toleransı: yükseklik, mekanik stres ve kablo çekme kuvveti dikkate alınmalı.

- Üretim notu: konektör yönü, lehim tipi ve kritik mekanik notlar şematik/üretim çiziminde açık olmalı.

Hızlı denetim:

- Seçilen konektör için karşı parça kodu ve fit testi doğrulandı mı?

- PCB kalınlığı ve mekanik toleranslar datasheet sınırları içinde mi?

- Ters takılma riskini önleyen mekanik anahtarlama mevcut mu?

40. Mekanik sabitleme pinlerinin durumu tanımlı mı?

Bazı bileşenlerde (örneğin büyük konektörler, tuş takımları, modüller) bulunan mekanik sabitleme pinleri, toprak (GND) hattına bağlanabilir veya elektriksel olarak izole edilmelidir. Bu karar tasarım aşamasında netleştirilmeli ve PCB üretim dosyalarında açıkça gösterilmelidir. Boşta bırakılan veya yanlış bağlanan sabitleme pinleri, hem EMC hem de mekanik dayanım açısından risk oluşturur.

Sabitleme pinleri için karar kuralları:

- Elektriksel rol tanımı: pinin yalnızca mekanik mi yoksa ekranlama/şasi fonksiyonu da mı olduğu netleştirilmeli.

- Bağlantı seçimi: şasi/koruyucu toprak bağlantısı gerekiyorsa doğrudan veya kontrollü empedansla (RC/0R) bağlanmalı.

- İzolasyon gereksinimi: floating bırakılacaksa bunun gerekçesi ve güvenlik etkisi notlanmalı.

- Mekanik dayanım: lehim pad boyutu ve ankraj yapısı beklenen mekanik yüke uygun olmalı.

- EMI etkisi: shield pinlerin GND’ye bağlanma noktası EMC performansını destekleyecek şekilde seçilmeli.

Hızlı denetim:

- Tüm sabitleme/shield pinlerinin bağlantı kararı şematikte açıkça belirtilmiş mi?

- Mekanik pinlerin yanlışlıkla sinyal nette bırakılması gibi hatalar temizlendi mi?

- EMC testlerinde shield/sabitleme bağlantı stratejisi hedef performansı sağlıyor mu?

41. EMC önlemleri (RC snubber, ferrit bead) kritik hatlarda şematikte gösterildi mi?

Elektromanyetik uyumluluk (EMC) için kullanılan tüm pasif filtreleme elemanları (RC snubber, ferrit bead, common-mode choke vb.) şematikte görünür olmalıdır. Bu elemanlar, özellikle hızlı anahtarlamalı güç hatları, motor sürücüleri ve clock sinyalleri için gereklidir. Filtre devrelerinin konumu ve değeri, üretim sırasında veya revizyonlarda karışıklık yaşanmaması için not olarak belirtilmelidir.

EMC önlemlerinde uygulanacak minimum çerçeve:

- Kritik hat tanımı: EMI kaynağı olabilecek hatlar (switch node, clock, motor, uzun kablo) listelenmeli.

- Filtre elemanları: RC snubber, ferrit, common-mode choke gibi elemanların amacı ve değeri belirtilmeli.

- Opsiyonel tuning: prototipte ince ayar için DNP/opsiyonel footprint bırakılmalı.

- Yerleşim notu: filtrelerin etkin olacağı konum (kaynağa yakın/arayüze yakın) açıkça yazılmalı.

- Test bağı: EMC test sonuçlarıyla filtre seçimleri arasında izlenebilir bağ kurulmalı.

Hızlı denetim:

- Kritik hatların hepsinde uygun EMC önlemi tanımlı mı?

- EMC testinde sorun çıkan hatlar için tuning opsiyonu mevcut mu?

- Filtre değerleri ve konumları üretim dosyalarında net şekilde aktarılmış mı?

Analog, RF ve Sinyal Bütünlüğü

42. Op-amp stabilitesi ve ortak-mod aralığı doğrulandı mı?

Op-amp devrelerinde kararlılık (stabilite), kazanç-bant genişliği (GBW), slew rate ve sıcaklık değişimlerine karşı davranış parametreleri kontrol edilmelidir. Kullanılan geri besleme topolojisine göre faz marjı ve osilasyon riski analiz edilmelidir. Ayrıca giriş sinyalleri op-amp'ın ortak-mod gerilim aralığı içinde kalmalıdır; aksi halde lineer çalışma bozulur. Bu kontroller, özellikle sensör arayüzleri ve ölçüm devrelerinde doğruluk için kritiktir.

Op-amp doğrulamasında aşağıdaki minimum kontrolleri uygulayın:

- Ortak-mod aralık: giriş sinyali tüm çalışma koşullarında op-amp

Vcmsınırları içinde kalmalı. - Çıkış salınımı: çıkışın yük altında rail’e yaklaşım sınırı (headroom) doğrulanmalı.

- Faz marjı: geri besleme topolojisinde hedef faz marjı tipik olarak

>45°olmalı. - Kazanç-bant/SR: GBW ve slew rate, en yüksek frekans ve genlik gereksinimini karşılamalı.

- Kapasitif yük etkisi: ADC sample-hold veya kablo kapasitesi gibi yüklerde kararlılık kontrol edilmeli.

Hızlı denetim:

- Worst-case sıcaklık/gerilimde op-amp doyuma giriyor mu?

- Simülasyon/ölçümde osilasyon veya ring gözleniyor mu?

- Gürültü ve offset bütçesi hedef ölçüm doğruluğunu karşılıyor mu?

43. Osilatör / clock enerjilenmesi kontrol edildi mi?

Tüm osilatör, kristal ve clock kaynaklarının güç hatları, üretici önerilerine göre filtrelenmeli ve besleme kararlılığı sağlanmalıdır. Zayıf besleme veya yetersiz bypass, clock jitter'ına ve iletişim senkronizasyon hatalarına yol açabilir. Bu durum özellikle MCU, RF transceiver veya yüksek hızlı haberleşme (örneğin USB, Ethernet) hatlarında sistemsel kararsızlık yaratır.

Clock bloğu için tasarım disiplini:

- Temiz besleme: osilatör/kristal beslemesi mümkünse ayrı filtre (ferrit + bypass) ile izole edilmeli.

- Bypass seti: saat kaynağına yakın

100nF+ gerektiğinde1uFkapasite kullanılmalı. - Yük kapasiteleri: kristal load capacitor değerleri datasheet/CL hesabına göre seçilmeli.

- Enable/reset bağımlılığı: clock kaynağının devreye giriş sırası güç ve reset senaryosuyla uyumlu olmalı.

- Yedek saat: kritik sistemlerde clock fault veya fallback clock stratejisi tanımlanmalı.

Hızlı denetim:

- Clock hattında beklenen frekans ve genlik ölçümde doğrulanıyor mu?

- Jitter/sapma haberleşme protokollerinin toleransını aşıyor mu?

- Besleme dalgalanması clock stabilitesini bozuyor mu?

44. Crosstalk ve parazit etkileri değerlendirildi mi?

Analog, dijital ve yüksek frekanslı hatlar arasında istenmeyen sinyal geçişi (crosstalk) analiz edilmelidir. Uzun paralel izlerden kaçınılmalı, gerekli durumlarda diferansiyel yönlendirme veya toprak referans hattı kullanılmalıdır. Empedans kontrollü hatlarda, iz uzunlukları ve dielektrik kalınlığı da sinyal bütünlüğü açısından gözden geçirilmelidir. Bu analiz, özellikle ADC girişlerinde, RF sinyallerde ve yüksek hızlı veri hatlarında hayati önem taşır.

Parazit/crosstalk için pratik kurallar:

- Paralel iz mesafesi: kritik hatlarda paralel uzunluk minimize edilmeli, gerekirse katman/mesafe ayrımı yapılmalı.

- Referans düzlem sürekliliği: yüksek hızlı sinyaller sürekli GND referansıyla yönlendirilmeli.

- Ayırma: analog girişler clock/switching hatlarından fiziksel olarak uzak tutulmalı.

- Diferansiyel eşleşme: diferansiyel çiftlerde uzunluk ve empedans eşleşmesi korunmalı.

- Gerekli filtreleme: hassas düğümlerde seri direnç/RC low-pass ile bant sınırlama değerlendirilmeli.

Hızlı denetim:

- Yakın paralel giden kritik izlerde crosstalk riski değerlendirildi mi?

- SI/PI incelemesinde sınırları aşan ringing/overshoot var mı?

- ADC veya hassas analog düğümlerde dijital aktiviteye bağlı gürültü gözleniyor mu?

45. RF hatları için via kalkanlama notlandı mı?

RF izleri, özellikle 2.4 GHz ve üzeri frekanslarda, çevresel etkilerden korunmak için via stitching (topraklama delikleriyle kalkanlama) tekniğiyle çevrelenmelidir. Bu uygulama, PCB katmanları arası RF sızıntısını azaltır ve empedans sürekliliğini korur. Şematikte bu gereklilik açıkça not edilmelidir; aksi halde yönlendirme sırasında gözden kaçabilir.

RF yönlendirme notlarında aşağıdaki detaylar yer almalı:

- Via fence kuralı: RF hattı boyunca düzenli aralıkla GND stitching via kullanımı belirtilmeli.

- Empedans hedefi: tek uçlu/diferansiyel hat için hedef empedans değeri notlanmalı.

- Geçiş sayısı: katman geçişleri minimumda tutulmalı; zorunlu via geçişleri simetrik planlanmalı.

- GND sürekliliği: RF hattının altında kesintisiz referans düzlem şartı açıkça yazılmalı.

- Anten çevresi: anten keep-out/metal boşluğu kuralları şematik notu veya layout notuyla bağlanmalı.

Hızlı denetim:

- RF hattı için via stitching ve keep-out notları layout ekibine açık aktarılmış mı?

- Empedans hesap hedefi üretici/anten gereksinimiyle uyumlu mu?

- Prototipte RF performansı (S11, menzil, link budget) beklenen aralıkta mı?

46. FET kapısı sürüşleri ve aşırı gerilim koşulları incelendi mi?

MOSFET veya benzeri güç elemanlarının gate hatları, hem sürücü direnci (gate resistor) hem de aşırı gerilim koruması açısından değerlendirilmelidir. Ani geçişlerde gate kapasitesi nedeniyle oluşabilecek salınımlar, hem EMC hem de termal stres açısından risk taşır. Bu nedenle snubber devresi, TVS diyot veya zener clamping çözümleri gerekli durumlarda uygulanmalıdır.

FET gate sürüşünde kritik kontrol maddeleri:

- Gate direnç seçimi: açma/kapama hızı ve EMI dengesine göre

Rgatedeğeri optimize edilmeli. - Vgs sınırı: gate-source gerilimi mutlak maksimum değeri aşmayacak şekilde clamp/zenner değerlendirilmeli.

- Miller etkisi: yüksek dv/dt koşullarında yanlış tetikleme riskine karşı gate pull-down/miller clamp düşünülmeli.

- Sürücü akımı: gate charge (

Qg) ve hedef anahtarlama süresine göre driver kapasitesi doğrulanmalı. - Snubber gereksinimi: drain dalgalanması/overshoot ölçülerek RC snubber ihtiyacı belirlenmeli.

Hızlı denetim:

- Ölçümde Vgs ve Vds pikleri güvenli sınırlar içinde mi?

- Gate dalgaformunda aşırı ring veya yanlış tetikleme var mı?

- Isınma/EMI sonuçları gate sürüş optimizasyonu sonrası iyileşiyor mu?

47. Arıza senaryolarında güç yarıiletkenleri değerlendirildi mi?

Kısa devre, yük kopması veya aşırı sıcaklık gibi arıza durumlarında, MOSFET, IGBT veya driver entegreleri üzerinde oluşabilecek enerji boşalım senaryoları analiz edilmelidir. Termal dayanım, SOA (Safe Operating Area) sınırları ve koruma topolojileri (örneğin akım sınırlama, aşırı ısı koruması, sigorta) tanımlanmalıdır. Bu kontroller, uzun ömürlü ve güvenli bir güç sisteminin temelini oluşturur.

Arıza senaryosu analizinde şu başlıklar zorunlu olmalı:

- SOA doğrulaması: yarıiletkenin gerilim-akım-zaman noktaları SOA grafiği içinde kalmalı.

- Kısa devre koruması: akım algılama, foldback veya hızlı kapatma (desat/ocp) mekanizması tanımlanmalı.

- Termal kapanma: aşırı sıcaklık senaryosunda güvenli shut-down ve yeniden başlatma davranışı belirlenmeli.

- Yük kopması/indüktif darbe: serbest dolaşım yolu, snubber ve clamp elemanları yeterli olmalı.

- Sigorta koordinasyonu: elektronik koruma ile sigorta açma eğrisi birbirini tamamlayacak şekilde seçilmeli.

Hızlı denetim:

- Worst-case arıza noktasında SOA ihlali oluşuyor mu?

- Kısa devre testinde eleman hasar almadan koruma devreye giriyor mu?

- Termal testlerde junction sıcaklığı güvenli sınırlar içinde kalıyor mu?

48. Stack-up ve empedans hedefleri şematik notlarında belirtildi mi?

PCB üretimi öncesinde katman yapısı (stack-up), empedans hedefleri, iz genişlikleri ve dielektrik kalınlıkları şematik notlarında belirtilmelidir. Bu bilgiler, üreticiyle teknik iletişimde karışıklığı önler. Örneğin: "50 Ω single-ended, 100 Ω differential, 1.6 mm FR-4, 4-layer stack-up" gibi net değerler, üretim doğruluğunu garanti altına alır.

Stack-up notlarında bulunması gereken minimum bilgiler:

- Katman dizilimi: katman sırası, bakır kalınlığı ve dielektrik tipleri belirtilmeli.

- Empedans hedefi: single-ended/differential hedefleri ve tolerans aralığı yazılmalı.

- Kritik hat sınıfı: empedans kontrollü net sınıfları (USB, Ethernet, RF vb.) listelenmeli.

- Üretici koordinasyonu: hedef değerlerin üretici stack-up teklifine göre teyidi notlanmalı.

- Revizyon etkisi: katman değiştiğinde empedans hesaplarının yeniden yapılacağı belirtilmeli.

Hızlı denetim:

- Şematik notlarında stack-up ve empedans hedefleri açıkça mevcut mu?

- Kritik net sınıfları doğru empedans hedefiyle eşleştirilmiş mi?

- Üretici geri dönüşü ile hedef değerler doğrulanmış mı?

49. Hassas ADC / DAC hatlarında temiz ve kirli GND ayrımı tanımlandı mı?

Analog ölçüm doğruluğunu korumak için AGND (analog ground) ve DGND (dijital ground) ayrımı yapılmalı, bu noktalar yalnızca tek bir referans noktasında (star ground) birleştirilmelidir. Bu ayrım, ADC ve DAC hatlarında dijital gürültünün analog sinyallere karışmasını engeller. Ayrıca güç ve sinyal yönlendirme planlarında da bu ayrım korunmalıdır.

ADC/DAC zemin ayrımında uygulanacaklar:

- Net ayrımı: AGND ve DGND şematikte ayrı net isimleriyle tanımlanmalı.

- Tek birleşim noktası: star-point lokasyonu açıkça işaretlenmeli.

- Referans koruması: ADC referans hattı dijital dönüş akımından uzak tutulmalı.

- Filtreleme: analog besleme ve referans hatlarında uygun RC/ferrit filtreleme uygulanmalı.

- Yerleşim notu: layout tarafında bölgesel ayrım ve dönüş yolu stratejisi notlanmalı.

Hızlı denetim:

- AGND/DGND ayrımı ve birleşim noktası şematikte net mi?

- ADC ölçümlerinde dijital aktiviteye bağlı gürültü baskın mı?

- Referans hattı düşük gürültülü dönüş yolunu koruyor mu?

Arabirimler ve Haberleşme

50. UART / SPI / I²C zamanlama ve seviye uyumları doğrulandı mı?

Tüm haberleşme hatları, bağlı cihazların zamanlama (timing) ve lojik seviye (voltage level) gereksinimlerine göre kontrol edilmelidir. Örneğin, bir sensör 3.3 V lojik seviyesinde çalışırken, mikrodenetleyici 5 V seviyesinde olabilir — bu durumda seviye çevirici (level shifter) veya direnç bölücü kullanılması gerekir. Ayrıca, veri geçişleri her cihazın setup/hold süreleri ve maksimum clock frekansları ile uyumlu olmalıdır. Bu kontrol, haberleşme hatalarının en yaygın kaynağını ortadan kaldırır.

Zamanlama ve seviye doğrulamasında şu adımları uygulayın:

- Seviye uyumu: her hat için

VIH/VIL/VOH/VOLdeğerleri karşı uç toleransını sağlamalı. - Timing bütçesi: setup/hold, rise/fall ve propagation delay toplamı protokol penceresine sığmalı.

- Level shifting kararı: farklı voltaj domainlerinde uygun topoloji (MOSFET, buffer, translator IC) seçilmeli.

- Topoloji etkisi: uzun kablo, konektör ve ESD elemanlarının zamanlama üzerindeki etkisi hesaba katılmalı.

- Boot durumu: açılışta hatların varsayılan seviyeleri protokol ihlaline neden olmamalı.

Hızlı denetim:

- Arabirim pin seviyeleri datasheet karşılaştırmasında uyumlu mu?

- Ölçümde setup/hold ihlali veya kenar bozulması görülüyor mu?

- Seviye çevirici kullanılan hatlarda yön/gecikme davranışı doğrulandı mı?

51. Baud ve clock seçimi doğru mu?

Seri haberleşme protokollerinde (özellikle UART), seçilen baud rate değeri, mikrodenetleyici saat frekansı ile uyumlu olmalı ve hata oranı düşük olmalıdır. %2'nin üzerindeki baud sapmaları, özellikle uzun kablolar veya düşük toleranslı alıcılarla sorun yaratabilir. SPI ve I²C gibi senkron protokollerde ise clock frekansı, bağlı cihazların maksimum hız parametrelerine göre belirlenmelidir. Doğru hız seçimi, hem veri bütünlüğünü hem de güç tüketimini doğrudan etkiler.

Saat/baud seçimi için pratik çerçeve:

- UART hata oranı: toplam baud hatası mümkünse

%1altında, zorunlu durumlarda%2altında tutulmalı. - SPI frekansı: slave cihazın

fSCK maxve setup/hold limitlerine göre güvenlik marjıyla seçilmeli. - I²C modu: Standard/Fast/Fast+ seçimi hat kapasitansı ve pull-up tasarımıyla birlikte yapılmalı.

- Saat kaynağı kararlılığı: osilatör toleransı + sıcaklık sapması toplam zamanlama bütçesine dahil edilmeli.

- EMI dengesi: gerekmedikçe maksimum hız yerine yeterli hız seçilerek kenar kaynaklı EMI azaltılmalı.

Hızlı denetim:

- Hesaplanan baud/frekans değerleri tüm bağlı cihazların sınırları içinde mi?

- Protokol analizöründe framing/parity/clock hata oranı kabul edilebilir düzeyde mi?

- Uzun kablo veya düşük sıcaklık/yüksek sıcaklıkta iletişim kararlılığı korunuyor mu?

52. I/O hatlarında küçük filtreleme (33 pF vb.) öngörüldü mü?

Dijital I/O hatlarına seri eklenen küçük kapasitörler (örneğin 22–47 pF), yüksek frekanslı gürültüleri bastırarak sistemin EMI/EMC dayanıklılığını artırır. Bu tür filtreleme elemanları, özellikle uzun kablo bağlantılarında veya harici sensör hatlarında iletişim güvenliğini artırır. Ancak kapasitans değeri, sinyalin yükselme süresini bozmayacak şekilde dikkatle seçilmelidir.

Küçük filtreleme elemanlarında şu dengeyi koruyun:

- Fonksiyon önceliği: filtreleme, protokol zamanlamasını bozmayacak noktada tutulmalı.

- RC hesabı: hat direnci + ek kapasite ile oluşan zaman sabiti sinyal bütçesine uygun olmalı.

- Uygulama alanı: dış dünyaya çıkan, uzun iz/kablo taşıyan veya hızlı kenarlı hatlarda öncelik verilmeli.

- Yerleşim: filtre elemanı gürültü kaynağına veya konektöre yakın konumlandırılmalı (amacına göre).

- Opsiyonel footprint: prototipte tuning için DNP/opsiyonel RC footprint bırakılması tavsiye edilir.

Hızlı denetim:

- Filtre sonrası kenar süreleri protokol limitleri içinde mi?

- EMI testinde ilgili hatlarda iyileşme gözleniyor mu?

- Filtre elemanı eklenince fonksiyonel hata (timeout, data corruption) oluşuyor mu?

53. Analog hatlar dijital hatlardan uzak mı?

Analog sinyaller, özellikle düşük seviye ölçüm hatları (örneğin sensör çıkışları veya ADC girişleri), dijital clock veya yüksek frekanslı sinyallerden fiziksel olarak ayrılmalıdır. Bu ayrım, PCB yönlendirme stratejisinde de sürdürülmeli ve analog hatlar tercihen ayrı bir referans düzlemi (AGND) üzerinde çalışmalıdır. Bu önlem, parazit geçişlerini azaltır ve ölçüm doğruluğunu artırır.

Analog-dijital ayrımda uygulanacak temel kurallar:

- Fiziksel mesafe: analog girişler, yüksek dv/dt taşıyan dijital/switching hatlardan uzak tutulmalı.

- Referans bütünlüğü: analog hatların altında mümkünse kesintisiz AGND referansı korunmalı.

- Geçiş yönetimi: analog ve dijital bölgeler arası zorunlu geçişler tek noktada ve kontrollü yapılmalı.

- Filtreleme: ADC girişinde uygun anti-alias RC filtresi ve kaynak empedansı uyumu sağlanmalı.

- Koruma: harici analog girişlerde ESD/overvoltage koruması ölçüm doğruluğunu bozmayacak şekilde seçilmeli.

Hızlı denetim:

- ADC ölçümlerinde dijital aktiviteye bağlı periyodik gürültü görülüyor mu?

- Analog hatların dönüş akımı gürültülü dijital GND yolunu paylaşıyor mu?

- Bölgeleme ve referans düzlem stratejisi layout incelemesinde tutarlı mı?

Varyant Yönetimi ve Modülerlik

54. Varyantlı kartlarda parça tak/çıkar durumu işaretlendi mi?

Birden fazla ürün varyantı (örneğin "Pro", "Lite" veya "OEM" sürümleri) aynı PCB üzerinden yönetiliyorsa, her varyant için parça tak/çıkar (DNP – Do Not Populate) durumu açıkça belirtilmelidir. Bu bilgiler, hem şematikte hem de varyant bazlı BoM (Bill of Materials) dokümanında tanımlanmalıdır. Net işaretlemeler, üretim sırasında karışıklığı önler ve hatasız montaj sağlar. Ayrıca, CAD sistemlerinde varyant yönetimi özelliği kullanılıyorsa, her konfigürasyon için üretim dosyaları ayrı olarak oluşturulmalıdır.

Varyant yönetiminde aşağıdaki standardı uygulayın:

- Varyant kodu: her ürün türevi için sabit kod kullanın (

BASE,LITE,PRO,OEM). - DNP işaretleme: her varyant için takılmayacak parçalar şematikte ve BoM’da aynı referansla belirtilmeli.

- Fonksiyon farkı tablosu: varyantlar arası elektriksel farklar (besleme, arabirim, opsiyonel modül) ayrı tabloda listelenmeli.

- Üretim çıktısı ayrımı: pick&place, BoM, test planı ve programlama dosyaları varyant bazında ayrı üretilmeli.

- Uyumluluk kontrolü: aynı PCB üzerinde varyantlar arası kısa devre/boşta pin/yanlış strap riski doğrulanmalı.

Hızlı denetim:

- Her varyant için tekil ve güncel BoM mevcut mu?

- DNP işaretleri şematik ile BoM arasında birebir uyuşuyor mu?

- Üretim dosyaları yanlış varyant karışmasını önleyecek şekilde ayrılmış mı?

55. Modül konektör montaj koşulları belirtildi mi?

Kart üzerinde harici modüller (örneğin GSM, Wi-Fi, GPS, sensör veya güç modülleri) kullanılıyorsa, bu konektörlerin montaj yönü, yüksekliği, lehimleme türü (SMT / TH) ve mekanik destek gereksinimleri şematikte veya not alanında açıkça belirtilmelidir. Bu bilgiler, üretim sırasında doğru konumlandırmayı sağlar ve özellikle manuel montaj veya prototip üretimi sırasında hataları azaltır.

Modül konektörleri için zorunlu montaj bilgileri:

- Yön bilgisi: pin-1 yönü ve mekanik referans noktası açıkça yazılmalı.

- Z yükseklik: modül-kart arası yükseklik ve keep-out sınırları belirtilmeli.

- Lehim tipi:

SMT/TH, lehim pastası ve gerekirse selektif lehim notu tanımlanmalı. - Mekanik destek: titreşim/çekme yükü için vida, standoff veya ankraj gereksinimi belirtilmeli.

- Servis erişimi: modül sök-tak senaryosunda erişim ve tolerans bilgisi notlanmalı.

Hızlı denetim:

- Montaj yönü ve pin-1 işareti üretim dokümanlarında net mi?

- Keep-out/height limitleri mekanik tasarımla çakışmıyor mu?

- Prototipte modül oturma/bağlantı güvenilirliği fiziksel testle doğrulandı mı?

56. Farklı PCB'lerde pin sıralaması tutarlı mı?

Birden fazla PCB veya alt modül içeren sistemlerde, aynı arabirim veya konektörün pin dizilimi tutarlı olmalıdır. Pin sıralamasındaki küçük farklar bile, kablo setlerinde veya test jig'lerinde ciddi hata ve hasarlara yol açabilir. Bu nedenle, tüm alt kartlar arasında ortak konektör standardı oluşturmak uzun vadeli bakım, üretim ve servis kolaylığı sağlar.

Çok kartlı sistemlerde pin tutarlılığı için:

- Master pinout dokümanı: sistem genelinde tek bir referans pinout tablosu tutulmalı.

- Adlandırma birliği: aynı sinyal her kartta aynı isimle geçmeli (

UART_DBG_TXgibi). - Yön netliği: kartlar arası sinyal yönü (

IN/OUT/BIDIR) tabloya eklenmeli. - Revizyon etkisi: bir kartta pin değişikliği olduğunda bağlı tüm kart/dokümanlar eşzamanlı güncellenmeli.

- Test-jig uyumu: pin dizilimi test fixture ve kablo harness ile çapraz doğrulanmalı.

Hızlı denetim:

- Kartlar arası konektör pin map karşılaştırmasında fark var mı?

- Aynı arabirim için isim/yön uyuşmazlığı bulunuyor mu?

- Revizyon sonrası eski kablo veya test jig ile uyumsuzluk riski analiz edildi mi?

57. Kritik hatlara 0Ω jumper eklendi mi?

Kritik veya kararsız sinyal hatlarında, 0 ohm direnç (jumper) kullanmak tasarım esnekliği sağlar. Bu elemanlar, ilerleyen revizyonlarda test, ölçüm veya alternatif bağlantı senaryoları için hızlı değişiklik yapılmasına imkân tanır. Ayrıca, üretim varyantları veya hata ayıklama süreçlerinde kart üzerinde kolay modifikasyon yapılmasını destekler.

0Ω jumper kullanımında doğru uygulama:

- Amaç tanımı: her 0Ω elemanı için kullanım amacı belirtilmeli (izolasyon, ölçüm, seçenek, rework).

- Konum seçimi: kritik hat kesme/ayırma noktasına en yakın yere yerleştirilmeli.

- Sinyal etkisi: yüksek hızlı hatlarda parasitik etkiler değerlendirilmeden 0Ω eklenmemeli.

- Varyant yönetimi: opsiyonel bağlantılarda 0Ω/DNP durumu varyant BoM ile eşleştirilmeli.

- Servis kolaylığı: debug sırasında kolay erişim için fiziksel konum ve işaretleme net olmalı.

Hızlı denetim:

- Kritik debug/izolasyon noktalarında gerekli 0Ω opsiyonları mevcut mu?

- 0Ω elemanları yanlışlıkla sinyal bütünlüğünü bozacak yerde konumlanmış mı?

- Üretim varyantlarında 0Ω montaj durumu açık ve tutarlı mı?

Bileşen Seçimi ve Yaşam Döngüsü

58. Kutuplu bileşen yönleri doğru mu?

Tüm kutuplu (polarize) bileşenlerin (örneğin elektrolitik kondansatör, tantal kondansatör, diyot, LED) yönleri şematikte ve PCB üzerinde doğru tanımlanmalıdır. Ters besleme, özellikle elektrolitik ve tantal kondansatörlerde kalıcı hasara, patlamaya veya kartın zarar görmesine neden olabilir. Bu nedenle kutuplar, hem sembol hem de yerleşim katmanında net şekilde işaretlenmeli, üretim dosyalarına açık not olarak eklenmelidir.

Kutuplu bileşen doğrulamasında uygulanacak kurallar:

- Sembol doğruluğu: anot/katot ve

+/-kutup işaretleri sembolde açıkça görünmeli. - Footprint eşleşmesi: PCB footprint pin-1/kutup işaretleri şematikle birebir uyuşmalı.

- Montaj işaretleri: silkscreen ve assembly layer üzerinde yön göstergesi bulunmalı.

- Ters besleme riski: kritik hatlarda yanlış montaja karşı koruma (seri diyot, anahtarlama vb.) değerlendirilmeli.

- Üretim talimatı: kutuplu parçalar için AOI/ICT kontrol kriterleri üretim dokümanına eklenmeli.

Hızlı denetim:

- Şematikte kutuplu tüm parçalar net yön etiketi taşıyor mu?

- Footprintte polarite işareti eksik veya çelişkili parça kaldı mı?

- İlk montaj numunesinde kutup hatası oranı sıfıra yakın mı?

59. Komponent voltaj / akım / sıcaklı koşulları uyumlu mu?

Her bileşenin maksimum çalışma voltajı, akımı ve sıcaklık aralığı, devrenin en kötü (worst-case) koşullarıyla karşılaştırılmalıdır. Bileşenlerin sürekli olarak sınır değerlerde çalışması, güvenilirliği ciddi biçimde düşürür. Tasarımda güvenlik payı bırakmak için genellikle bileşenler, nominal koşulların %70–80 kapasitesi civarında kullanılmalıdır. Ayrıca, yüksek sıcaklık ortamlarında derating (değer düşürme) hesapları yapılmalıdır.

Boyutlandırma disiplini:

- Gerilim marjı: bileşen gerilim limiti, çalışma tepe gerilimine karşı uygun güvenlik payı içermeli.